Povećavanje brzine izvršavanja programa posljedično povećava brzinu programa procesor. Izumljeno je mnogo načina, kako hardverska implementacija, tako i softverska arhitektura, kako bi se povećala brzina izvršavanja. Primijećeno je da se istodobnim izvršavanjem uputa može smanjiti vrijeme potrebno za izvršenje. Koncept paralelizma u programiranje je predložen. Prema tome, više ciklusa može se izvršiti po taktu. Ovaj koncept programer može prakticirati kroz razne tehnike kao što su Cjevovodi, više izvedbenih jedinica i više jezgri . Među svim tim paralelnim metodama najčešće se prakticira cjevovod. Pa kako se uputa može izvršiti metodom cjevovoda? Kako to povećava brzinu izvršenja?

Što je cjevovod?

Da bismo shvatili koncept cjevovoda, pogledajmo korijensku razinu izvršavanja programa. Uputa je najmanji izvršni paket programa. Svaka uputa sadrži jednu ili više operacija. Jednostavni skalarni procesori izvršavaju jednu ili više naredbi po taktu, pri čemu svaka naredba sadrži samo jednu operaciju. Upute se izvršavaju u slijedu faza kako bi se postigli očekivani rezultati. Ovaj je slijed dan u nastavku

Slijed izvršenja uputa

- IF: Dohvaća uputu u registar uputa.

- ID: Instruction Decode, dekodira upute za opcode.

- AG: Generator adresa, generira adresu.

- DF: Dohvaćanje podataka, dohvaća operande u podatkovni registar.

- EX: Izvršenje, izvršava navedenu operaciju.

- WB: Napiši natrag, upiši rezultat natrag registar.

Nisu sve upute potrebne za sve gore navedene korake, ali većina ih zahtijeva. Ovi koraci koriste različite hardverske funkcije. U cjevovodu se ove različite faze izvode istodobno. U cjevovodu se ove faze smatraju neovisnim između različitih operacija i mogu se preklapati. Dakle, istovremeno se može izvoditi više operacija, pri čemu je svaka operacija u svojoj neovisnoj fazi.

Upute za cjevovode

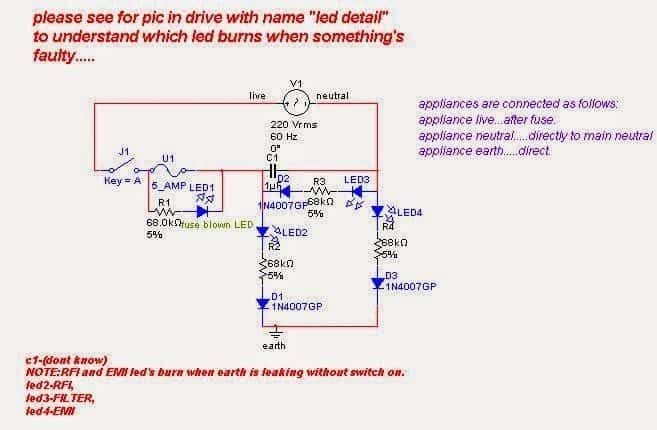

Pogledajmo način obrade uputa u cjevovodu. To se lako može razumjeti donjim dijagramom.

Upute za cjevovode

Pretpostavimo da su upute neovisne. U jednostavnom procesoru cjevovoda, u određeno vrijeme, postoji samo jedna operacija u svakoj fazi. Početna faza je IF faza. Dakle, u prvom ciklusu takta dohvaća se jedna operacija. Kad stigne sljedeći impuls takta, prva operacija prelazi u ID fazu, ostavljajući IF fazu praznom. Sada se ova prazna faza dodjeljuje sljedećoj operaciji. Dakle, tijekom drugog impulsa takta prva operacija je u fazi ID, a druga operacija je u fazi IF.

Za treći ciklus, prva operacija bit će u fazi AG, druga operacija bit će u fazi ID, a treća operacija bit će u fazi IF. Na taj se način instrukcije izvršavaju istodobno i nakon šest ciklusa procesor će izdati potpuno izvršene instrukcije po taktu.

Je li se ova uputa izvršavala sekvencijalno, u početku prva uputa mora proći kroz sve faze, a zatim će se dohvatiti sljedeća uputa? Dakle, za izvršenje svake naredbe procesoru bi trebalo šest ciklusa takta. Ali u procesoru s cjevovodom, jer se izvršavanje naredbi odvija istodobno, samo početna uputa zahtijeva šest ciklusa, a sve se preostale upute izvršavaju po jedan u svakom ciklusu, čime se smanjuje vrijeme izvršavanja i povećava brzina procesora.

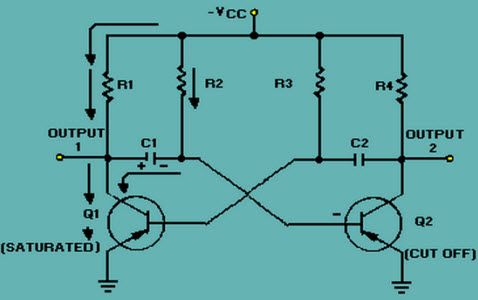

Cjevovodna arhitektura

Paralelizam se može postići hardverskim, kompajlerom i softverskim tehnikama. Da bi se iskoristio koncept cjevovoda u arhitektura računala mnoge procesorske jedinice međusobno su povezane i funkcioniraju istodobno. U cjevovodnoj arhitekturi procesora postoje odvojene procesne jedinice predviđene za cijele brojeve i upute s pomičnim zarezom. Dok je u sekvencijalnoj arhitekturi predviđena jedna funkcionalna jedinica.

Cjevovodna procesorska jedinica

U statičkom cjevovodu, procesor bi trebao prenositi uputu kroz sve faze cjevovoda bez obzira na zahtjev za uputama. U dinamičkom procesoru cjevovoda, uputa može zaobići faze ovisno o svojim zahtjevima, ali se mora kretati sekvencijalnim redoslijedom. U složenom dinamičkom procesoru cjevovoda, uputa može zaobići faze, kao i odabrati faze izvan reda.

Cjevovod u RISC procesorima

Najpopularniji RISC arhitektura ARM procesor slijedi trofazni i petostupanjski cjevovod. U trofaznom cjevovodu faze su: Dohvati, Dekodiraj i Izvrši. Ovaj cjevovod ima latenciju od 3 ciklusa, jer pojedinačna uputa traje 3 ciklusa sata.

ARM 3 stupanj cjevovod

Za pravilnu provedbu cjevovoda Hardversku arhitekturu također treba nadograditi. Hardver za trostupanjsko cjevovođenje uključuje banku registara, ALU, mjenjač cijevi, generator adresa, inkrementer, dekoder upute i registre podataka.

ARM 3 podatkovna staza za cjevovode

U 5 stupnjeva cjevovodno slaganje faza su: Dohvaćanje, Dekodiranje, Izvršenje, Međuspremnik / podaci i Nazad.

Opasnosti od cjevovoda

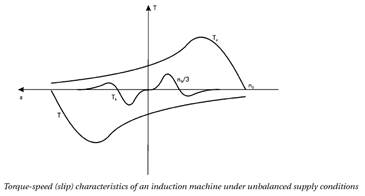

U tipičnom računalnom programu, osim jednostavnih uputa, nalaze se i upute za grane, operacije prekida, upute za čitanje i pisanje. Cjevovod nije prikladan za sve vrste uputa. Kada se neke upute izvrše u cjevovodu, mogu zaustaviti cjevovod ili ga potpuno isprati. Ova vrsta problema nastalih tijekom cjevovoda naziva se opasnost od cjevovoda.

U većini računalnih programa rezultat jedne instrukcije koristi se kao operand druge instrukcije. Kada se takve naredbe izvršavaju u cjevovodu, dolazi do raščlambe jer rezultat prve naredbe nije dostupan kad naredba dva započne sakupljati operande. Dakle, druga se uputa mora zaustaviti dok se ne izvrši prva uputa i generira rezultat. Ova vrsta opasnosti naziva se Read -after-write cjevovodna opasnost.

Čitaj nakon pisanja opasnosti od pipe

Izvršenje uputa za grane također uzrokuje opasnost od cjevovoda. Upute za grane dok su izvršene u cjevovodu utječe na faze dohvaćanja sljedećih uputa.

Ponašanje pipeliranog ogranka

Prednosti cjevovoda

- Povećava se protok uputa.

- Povećanje broja stupnjeva cjevovoda povećava broj istodobno izvršenih naredbi.

- Brži ALU može se dizajnirati kada se koristi cjevovod.

- Pipelined CPU radi na višim frekvencijama takta od RAM-a.

- Cjevovođenje povećava ukupne performanse CPU-a.

Nedostaci cjevovoda

- Projektiranje cjevovodnog procesora je složeno.

- Povećava se latencija uputa kod cjevovodnih procesora.

- Propusnost cjevovodnog procesora teško je predvidjeti.

- Što je duži cjevovod, to je gori problem opasnosti za upute za grane.

Cjevovod koristi svim uputama koje slijede sličan slijed koraka za izvršenje. Procesore koji imaju složene upute u kojima se svaka naredba ponaša drugačije od ostalih teško je provesti. Prerađivači imaju razumne uređaje s 3 ili 5 stupnjeva cjevovoda, jer kako se dubina cjevovoda povećava, opasnosti povezane s tim povećavaju se. Navedite neke od cjevovodnih procesora s njihovim stupnjem cjevovoda?