ECL (emiter spregnuta logika) prvi je izumio Hannon S. Yourke u IBM-u u kolovozu 1956. godine. Ova logika je također poznata kao logika trenutnog načina rada, koja se koristi u računalima IBM 7090 i 7094. Obitelj ECL je vrlo brza u usporedbi s digitalna logika obitelji. Općenito, ova logička obitelj osigurava kašnjenje širenja manje od 1 ns. To je logička obitelj koja se temelji na bipolarnim spojnim tranzistorima. To je najbrži sklop logičke obitelji koji je dostupan za projektiranje konvencionalnog logičkog sustava. Ovaj članak govori o pregledu emiter spregnut logički sklop , rad s aplikacijama.

Što je emiter spregnuta logika?

Emiter-spregnuta logika je najbolja BJT obitelj zasnovana na logici koja se koristi u dizajnu konvencionalnog logičkog sustava. Ponekad se također naziva logikom trenutnog načina rada koja je digitalna tehnologija vrlo velike brzine. Općenito, ECL se smatra najbržim logičkim integriranim sklopom gdje postiže rad velike brzine korištenjem vrlo malog zamaha napona i također izbjegavajući da tranzistori uđu u područje zasićenja.

Implementacija ECL-a koristi pozitivni napon napajanja koji je poznat kao PECL ili pozitivno referencirani ECL. U ranim ECL vratima koristi se negativni napon napajanja zbog otpornosti na šum. Nakon toga, pozitivno referencirani ECL postao je vrlo poznat zbog svojih kompatibilnijih logičkih razina u usporedbi s TTL logičkim obiteljima.

Emitersko spregnuta logika raspršuje ogromnu količinu statičke snage, međutim, njezina ukupna potrošnja struje niska je u usporedbi s CMOS na visokim frekvencijama. Dakle, ECL je uglavnom koristan u krugovima distribucije takta i visokofrekventnim aplikacijama.

Logičke značajke spregnute emiterom

Značajke ECL-a omogućit će njihovu upotrebu u mnogim aplikacijama koje se temelje na visokim performansama.

- ECL osigurava dva izlaza koji se međusobno uvijek nadopunjuju jer se rad kruga temelji na diferencijalnom pojačalu.

- Ova logička obitelj je uglavnom prikladna za monolitne metode izrade jer su logičke razine funkcija omjera otpornika.

- Uređaji iz obitelji ECL generiraju pravi i komplementarni izlaz predložene funkcije bez korištenja vanjskih pretvarača. Posljedično, smanjuje se broj paketa, zahtjevi za napajanjem i također smanjuju problemi koji nastaju zbog vremenskih kašnjenja.

- ECL uređaji u dizajnu diferencijalnog pojačala nude široku fleksibilnost performansi, tako da ECL krugovi omogućuju upotrebu i kao digitalni i kao linearni krugovi.

- Dizajn ECL vrata obično ima visoku i nisku ulaznu impedanciju, što je izuzetno pogodno za postizanje velikog ventilatora, kao i mogućnosti pogona.

- ECL uređaji stvaraju stalnu struju odvoda napajanja kako bi se pojednostavio dizajn napajanja.

- Uređaji ECL-a koji uključuju izlaze otvorenog emitera jednostavno im omogućuju da uključe pogonski kapacitet dalekovoda.

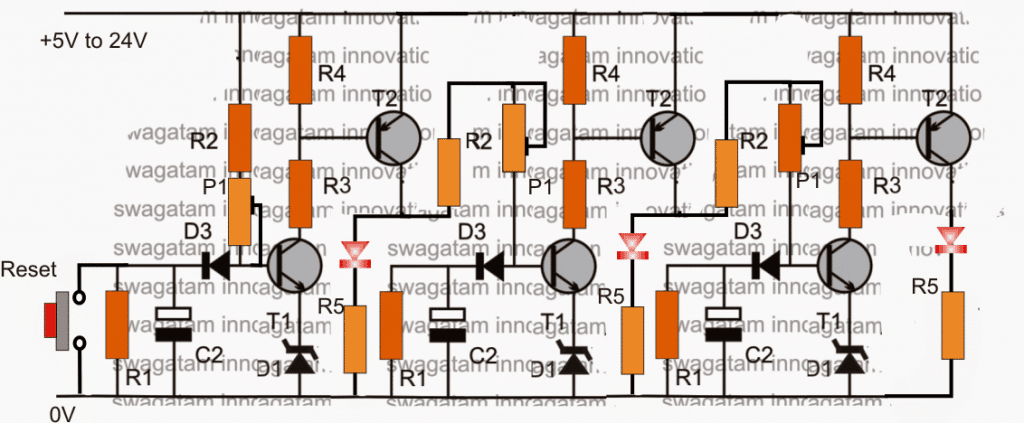

Emiterski spojeni logički krug

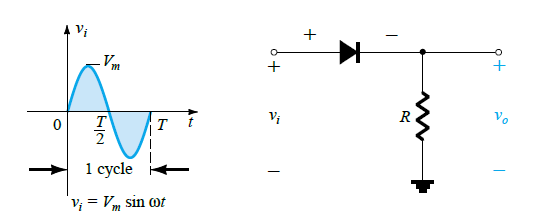

Emiter-spregnuti logički krug za pretvarač prikazan je u nastavku koji je dizajniran s otpornicima i tranzistorima. U ovom krugu, terminali emitera dvaju tranzistora jednostavno su spojeni na strujni ograničavajući otpor RE koji se koristi kako bi se izbjeglo da tranzistor uđe u zasićenje. Ovdje se izlaz tranzistora uzima s terminala kolektora umjesto terminala emitera. Ovaj sklop ima dva izlaza Vout (invertirajući izlaz) i Vout2 (neinvertirajući izlaz) i ulazni terminal poput Vin gdje se daje visoki ili niski ulaz. +Vcc = 5V.

Kako radi logika spojena emiterom?

Rad logike spregnute emiterom je da kad god se HIGH ulaz da ECL krugu, on će učiniti tranzistor 'Q1' ON i tranzistor Q2 OFF, ali tranzistor Q1 nije zasićen. Dakle, ovo će povući izlaz VOUT2 na HIGH, a vrijednost izlaza VOUT1 bit će LOW zbog pada unutar R1.

Slično, kada je VIN vrijednost dana ECL-u NISKA, tada će tranzistor Q1 biti ISKLJUČEN, a tranzistor Q2 UKLJUČEN. Dakle, tranzistor Q2 neće prijeći u zasićenje. Tako će izlaz VOUT1 biti VISOK, a izlazna vrijednost VOUT2 bit će niska zbog pada unutar otpora R2.

Pogledajmo kako se tranzistor Q1 i Q2 uključuje i isključuje kada se primijeni napon.

Dva tranzistora poput Q1 i Q2 u ovom krugu spojena su kao diferencijalno pojačalo pomoću zajedničkog otpornika emitera.

Napon napajanja za ovaj primjer kruga je VCC = 5,0, VBB = 4,0 & VEE = 0 V. Vrijednosti ulazne VISOKE i NIZE razine jednostavno su definirane na 4,4 V i 3,6 V. Zapravo, ovaj krug generira NISKI izlaz i VISOKE razine koje su za 0,6 V više; međutim, to se ispravlja unutar stvarnih ECL krugova.

Kada je Vin VISOK, tada je tranzistor Q1 uključen, ali nije zasićen i tranzistor Q2 je isključen. Dakle, izlazni napon poput VOUT2 se povlači na 5 V kroz otpornik R2 i može se pokazati da je pad napona na otporniku R1 oko 0,8 V tako da je VOUT1 = 4,2 V (NISKO). Uz to VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V jer je tranzistor Q1 potpuno uključen.

Nakon što je Vin NIZAK, Q2 tranzistor će biti uključen, ali neće biti zasićen i Q1 tranzistor će biti isključen. Stoga se VOUT1 povlači na 5,0 V pomoću otpornika R1 i može se pokazati da je VOUT2 4,2 V. Također VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V jer je tranzistor Q2 uključen.

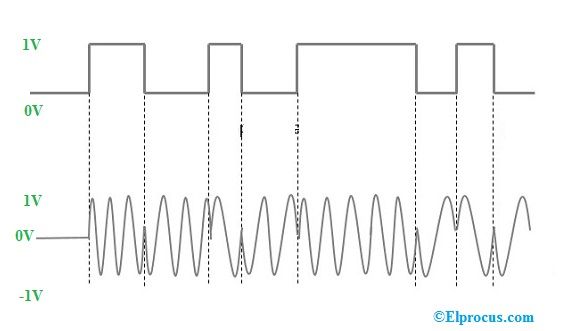

U ECL, dva tranzistora nikada nisu u zasićenju kao t Oscilacije ulaznog/izlaznog napona su prilično male poput 0,8 V a ulazna impedancija je visoka, a izlazni otpor nizak. To pomaže ECL-u da radi brže s manjim vremenom kašnjenja širenja.

Sklop logičkih ILI/NI vrata s dva ulaza emitera

Dolje je prikazan sklop s dva ulazna emitera spregnuta logička ILI/NI vrata. Ovaj krug je dizajniran modificiranjem gornjeg inverterskog kruga. Modifikacija je dodavanjem dodatnog tranzistora na ulaznoj strani.

Rad ovog sklopa je vrlo jednostavan. Kada su ulazi primijenjeni na oba tranzistora Q1 i Q2 niski tada će izlaz1 (Vout1) biti VISOKA vrijednost. Dakle, ovaj Vout1 odgovara izlazu NOR vrata.

Istovremeno, ako je tranzistor Q3 uključen, tada će drugi izlaz (Vout2) biti VISOK. Dakle, ovaj izlaz Vou2 odgovara izlazu OR vrata.

Na isti način, ako su oba ulaza tranzistora Q1 i Q2 VISOKI, tada će se uključiti tranzistori Q1 i Q2 i osigurati niski izlaz na terminalu VOUT1.

Ako je Q3 tranzistor ISKLJUČEN tijekom ove operacije tada će dati visok izlaz na VOUT2 terminalu. Dakle, tablica istine za ILI/NI vrata je dana ispod.

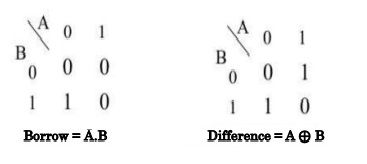

|

Unosi |

Unosi | ILI |

NI |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Logičke karakteristike spregnute emiterom

Karakteristike ECL-a uključuju sljedeće.

- U usporedbi s TTL-om, ECL ima brže vrijeme propagacije u rasponu od 0,5 do 2 ns. Ali disipacija snage povezane s emiterskom logikom veća je u usporedbi s TTL-om, poput 30 mW.

- I/O naponi ECL-a imaju mali zamah poput 0,8.

- Ulazna impedancija ECL-a je visoka, a izlazni otpor nizak; posljedično, tranzistor vrlo brzo mijenja svoja stanja.

- Kapacitet ventilatora ECL-a je visok, a kašnjenja vrata su mala.

- O/p logika ECL-a mijenja se iz LOW u HIGH stanje, ali će razine napona za ta stanja varirati između TTL i EC.

- Otpornost na buku ECL-a je 0,4 V.

Prednosti i nedostatci

The prednosti emitersko spregnute logike razmatraju se u nastavku.

- Fanout ECL-a je 25, što je bolje u usporedbi s TTL-om i nisko je u usporedbi s CMOS-om.

- Prosječno vrijeme kašnjenja širenja ECL-a je 1 do 4 ns, što je bolje u usporedbi s CMOS i

- TTL. Stoga se naziva najbržom logičkom obitelji.

- Kada su BJT u emiteru spojeni logička vrata rade u aktivnoj regiji, tada imaju najveću brzinu u usporedbi sa svim logičkim obiteljima.

- ECL vrata generiraju komplementarne izlaze.

- Preklopni skokovi struje nisu prisutni u vodovima napajanja.

- Izlazi se mogu spojiti zajedno kako bi se osigurala žična ILI funkcija.

- Parametri ECL-a se ne mijenjaju mnogo s temperaturom.

- Broj Funkcija dostupnih s jednog jedinog čipa je visoka.

The nedostaci emitersko spregnute logike razmatraju se u nastavku.

- Ima izuzetno nisku marginu šuma, tj. ±200 mV.

- Rasipanje snage je visoko u usporedbi s drugim logičkim vratima.

- Za sučelje s drugim logičkim obiteljima potrebni su mjenjači razine.

- Fanout ograničava kapacitivno opterećenje.

- U usporedbi s TTL , ECL vrata su skupa.

- U usporedbi s CMOS & TTL, ECL otpornost na šum je najgora.

Prijave

Primjene emitersko spregnute logike uključuju sljedeće.

- Emitter-coupled logika koristi se kao tehnologija logike i sučelja unutar komunikacijskih uređaja iznimno velike brzine kao što su sučelja primopredajnika s optičkim vlaknima, Ethernet & ATM (Asynchronous Transfer Mode) mreže.

- ECL je logička obitelj koja se temelji na BJT-u gdje se njegov brzi rad može postići korištenjem relativno malog zamaha napona i izbjegavanjem pomicanja tranzistora u područje zasićenja.

- ECL se koristi u izradi ASLT sklopova unutar IBM 360/91.

- ECL izbjegava korištenje naslaganih tranzistora korištenjem jednostranog biasa i/p i pozitivne povratne sprege između primarnih i sekundarnih tranzistora kako bi se postigla funkcija pretvarača.

- ECL se koristi u elektronici ekstremnih brzina.

Dakle, ovo je pregled emiterski spregnute logike ili ECL – krug, rad, značajke, karakteristike i primjene. ECL je vrlo najbrža logička obitelj temeljena na BJT u usporedbi s drugim digitalnim logičkim obiteljima. Svoju maksimalnu brzinu postiže korištenjem malog zaokreta napona i izbjegavanjem prelaska tranzistora u područje zasićenja. Ova logička obitelj pruža nevjerojatnu odgodu propagacije od 1 ns, au najnovijim ECL obiteljima ta je odgoda smanjena. Evo pitanja za vas, koji je alternativni naziv za ECL?