U domeni elektronike najvažniji koncept na kojem svaka komponenta radi je ' Logička vrata “. Kako se koncept logičkih ulaza implementira u svaku funkcionalnost, poput integriranih krugova, senzora, preklopnih svrha, mikrokontrolera i procesora, šifriranja i dešifriranja i drugih. Uz ove, postoje i široke primjene Logic Gatesa. Postoje mnoge vrste logičkih vrata kao što su zbrajanje, oduzimač, puni Guja , Puni oduzimač, Polovica oduzimača i mnogi drugi. Dakle, ovaj članak pruža zbirne informacije o krug pola oduzimača , pola oduzimača tablica istine , i srodni pojmovi.

Što je Half Subtractor?

Prije nego što krenemo u raspravu o poluoduzimaču, moramo znati binarno oduzimanje. U binarnom oduzimanju postupak oduzimanja sličan je aritmetičkom oduzimanju. U aritmetičkom oduzimanju koristi se osnovni sustav brojeva 2, dok se kod binarnog oduzimanja za oduzimanje koriste binarni brojevi. Rezultirajući pojmovi mogu se označiti razlikom i posuditi.

Polovica oduzimača je najvažnija kombinacijski logički sklop koji se koristi u digitalna elektronika . U osnovi, ovo je elektronički uređaj ili drugim riječima, možemo to reći kao logički sklop. Ovaj se krug koristi za oduzimanje dvije binarne znamenke. U prethodnom smo članku već razgovarali pojmovi napola zbrajanja i punog sklopa zbrajanja koja za izračun koristi binarne brojeve. Slično tome, sklop oduzimača koristi binarne brojeve (0,1) za oduzimanje. Krug napola oduzimača može se graditi s dva logička vrata, naime vrata NAND i EX-OR . Ovaj sklop daje dva elementa kao što su razlika kao i posuđivanje.

Kao i kod binarnog oduzimanja, glavna je znamenka 1, možemo generirati posuđivanje, dok je odštetnik 1 superiorniji od minuenda 0 i zbog toga će trebati posuđivanje. Sljedeći primjer daje binarno oduzimanje dva binarna bita.

Prva znamenka | Druga znamenka | Razlika | Posuditi |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

U gornjem oduzimanju, dvije znamenke mogu se predstaviti s A i B. Te dvije znamenke mogu se oduzeti i rezultirajuće bitove daju kao razliku i posuđivanje.

Kada promatramo prva dva i četvrti redak, razlika između ovih redaka, tada su razlika i posuđivanje slični jer je odštetnik manji od minuenda. Slično tome, kada promatramo treći redak, vrijednost minuenda oduzima se od oduzimanja. Dakle, bitovi razlike i posudbe su 1 jer je znamenka oduzimanja superiornija od znamenke minuend.

Ovaj kombinacijski krug je važan alat za bilo koju vrstu digitalni sklop da znaju moguće kombinacije ulaza i izlaza. Na primjer, ako oduzimač ima dva ulaza, tada će rezultatski izlazi biti četiri. O / p polovnog oduzimača spomenut je u donjoj tablici koja će označavati bit bita, kao i bit bita. Objašnjenje tablice istinitosti sklopa može se izvršiti korištenjem logičkih vrata kao što su logička vrata EX-OR i rad vrata AND nakon čega slijedi NOT gate.

Rješavanje tablice istine pomoću K-karta prikazano je dolje.

napola oduzimač k karta

The pola oduzimanja izraza pomoću tablice istine i K-mape može se izvesti kao

Razlika (D) = ( x’y + xy ')

= x ⊕ y

Posuditi (B) = x’y

Logički krug

The napola oduzimač logički sklop može se objasniti korištenjem logičkih vrata:

- 1 XOR kapija

- 1 NE vrata

- 1 I vrata

Zastupljenost je

Polovica oduzimača logički krug

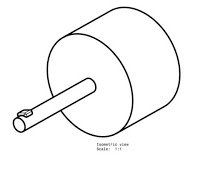

Blok dijagram s poluoduzimačem

Blok dijagram poluoduzimača prikazan je gore. Potrebna su dva ulaza, kao i dva izlaza. Ovdje su ulazi predstavljeni s A&B, a izlazi su Difference and Borrow.

Gornji krug može se projektirati s EX-OR & NAND vratima. Ovdje se NAND vrata mogu graditi pomoću vrata AND i NOT. Dakle, potrebna su nam tri logička vrata za izradu pola sklopa oduzimača, naime vrata EX-OR, NOT gate i NAND gate.

Kombinacija vrata AND i NOT daju različita kombinirana vrata nazvana NAND Gate. Izlaz Ex-OR vrata bit će bit razlike, a izlaz NAND ulaza bit bit Posudbe za iste ulaze A&B.

I-Vrata

AND-gate jedna je vrsta digitalnih logičkih vrata s više ulaza i jednim izlazom i na temelju kombinacija ulaza izvest će logičku konjukciju. Kad su svi ulazi ovih vrata visoki, tada će izlaz biti visok, u suprotnom izlaz će biti nizak. Logički dijagram AND vrata s tablicom istine prikazan je u nastavku.

I Tablica vrata i istine

NE Vrata

NOT-gate je jedna vrsta digitalnih logičkih vrata s jednim ulazom i na temelju ulaza izlaz će biti obrnut. Na primjer, kada je ulaz NOT vrata velika, izlaz će biti nizak. Logički dijagram NOT-vrata s tablicom istine prikazan je u nastavku. Korištenjem ove vrste logičkih vrata možemo izvršiti NAND i NOR vrata.

NE Vrata i tablica istine

Bivši ILI Vrata

Exclusive-OR ili EX-OR vrata jedna su vrsta digitalnih logičkih vrata s 2 ulaza i jednim izlazom. Rad ovih logičkih vrata ovisi o OR vratima. Ako je netko od ulaza ovog ulaza visok, tada će izlaz EX-OR vrata biti visok. Tablica simbola i istine EX-OR prikazani su u nastavku.

XOR Tabela vrata i istine

Polovica kruga oduzimača pomoću Nand Gatea

Projektiranje oduzimača može se izvesti do pomoću logičkih vrata poput vrata NAND i vrata Ex-OR. Da bismo dizajnirali ovaj pola oduzimajućeg kruga, moramo znati dva pojma, naime razlika i posuđivanje.

Polovica kruga oduzimača pomoću Nand Gatea

Ako budemo pažljivo pratili, prilično je jasno da je raznolikost operacija izvedenih ovim krugom koja je točno povezana s radom EX-OR vrata. Stoga, za razliku možemo jednostavno koristiti EX-OR vrata. Na isti način, posudba proizvedena u polusabiralnom krugu može se jednostavno postići korištenjem mješavine logičkih vrata poput AND-gate i NOT-gate.

Ovaj se HS također može projektirati korištenjem NOR vrata gdje je za izgradnju potrebno 5 NOR vrata. Poluoduzimač sheme spojeva koji koristi NOR vrata prikazan je kao:

Polovica oduzimača koji koristi niti vrata

Tablica istine

Prvi bit | Drugi bit | Razlika (EX-ILI van) | Posuditi (NAND izlaz) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL i Testbench kôd

VHDL kôd za polovinu oduzimača objašnjen je kako slijedi:

knjižnica IEEE

upotrijebite IEEE.STD_LOGIC_1164.ALL

upotrijebite IEEE.STD_LOGIC_ARITH.ALL

upotrijebite IEEE.STD_LOGIC_UNSIGNED.ALL

entitet Half_Sub1 je

Luka (a: u STD_LOGIC

b: u STD_LOGIC

HS_Diff: izlazi STD_LOGIC

HS_Sutra: izlazi STD_LOGIC)

kraj Half_Sub1

arhitektura Ponašanje Half_Sub1 je

početi

HS_Diff<=a xor b

HS_Sutra<=(not a) and b

The kôd testne ploče za HS objašnjeno je na sljedeći način:

KNJIŽNICA IEEE

KORISTITE ieee.std_logic_1164.ALL

ENTITY HS_tb JE

KRAJ HS_tb

ARHITEKTURA HS_tb OD HS_tb JE

KOMPONENTA HS

LUKA (a: U std_logic

b: U std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

KONAČNA KOMPONENTA

signal a: std_logic: = '0'

signal b: std_logic: = ‘0’

signal HS_Diff: std_logic

signal HS_Borrow: std_logic

POČETI

novo: HS PORT MAPA (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_posudba => HS_posudba

)

stim_proc: proces

početi

do<= ‘0’

b<= ‘0’

pričekajte 30 ns

do<= ‘0’

b<= ‘1’

pričekajte 30 ns

do<= ‘1’

b<= ‘0’

pričekajte 30 ns

do<= ‘1’

b<= ‘1’

čekati

završiti postupak

KRAJ

Potpuni oduzimač pomoću polovine oduzimača

Potpuni oduzimač kombinirani je uređaj koji upravlja funkcijom oduzimanja pomoću dva bita te je minuend i subtrahend. Krug smatra posuđivanjem prethodnog izlaza i ima tri ulaza s dva izlaza. Tri ulaza su minuend, subtrahend i input primljeni iz prethodnog izlaza koji je posuđen, a dva izlaza su razlika i posuđivanje.

Potpuni logički dijagram oduzimača

Tablica istine za puni oduzimač je

| Ulazi | Izlazi | |||

| x | Y | Yin | FS_Diff | FS_Sutra |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

S gornjom tablicom istine, dolje je prikazan logički dijagram i dijagram krugova za implementaciju punog oduzimača koji koristi polovinu oduzimača:

Potpuni oduzimač pomoću HS

Prednosti i ograničenja polovnog oduzimača

Prednosti polovnog oduzimača su:

- Implementacija i konstrukcija ovog kruga je jednostavna i laka

- Ovaj krug troši minimalnu snagu u digitalnoj obradi signala

- računske funkcionalnosti mogu se izvoditi s poboljšanim brzinama

Ograničenja ovog kombinacijskog kruga su:

Iako postoje opsežne primjene polovine oduzimača u mnogim operacijama i funkcionalnostima, malo je ograničenja, a to su:

- Krugovi napola oduzimača neće prihvatiti 'Uzajmljivanje' iz prethodnih izlaza, gdje je to presudni nedostatak ovog kruga

- Kako mnoge aplikacije u stvarnom vremenu rade na oduzimanju velikog broja bitova, pola uređaja za oduzimanje ne posjeduju mogućnost oduzimanja mnogih bitova

Primjene polovnog oduzimača

Primjene polovnog oduzimača uključuju sljedeće.

- Pola oduzimača koristi se za smanjenje sile audio ili radio signala

- To može biti koristi se u pojačalima za smanjenje izobličenja zvuka

- Polovica oduzimača je koristi se u ALU procesoru

- Može se koristiti za povećanje i smanjenje operatora, a također izračunava adrese

- Pola oduzimača koristi se za oduzimanje najmanje značajnih brojeva stupaca. Za oduzimanje višeznamenkastih brojeva može se koristiti za LSB.

Stoga, iz gornje polovice teorije oduzimača, napokon, možemo zaključiti da pomoću ovog sklopa možemo oduzeti jedan binarni bit od drugog kako bismo dobili izlaze poput Razlike i Posuđivanja. Slično tome, možemo dizajnirati polovinu oduzimača pomoću kruga NAND vrata, kao i NOR vrata. Ostali pojmovi koje treba znati su ono što je pola oduzimača verilog koda i kako se može nacrtati shematski dijagram RTL-a?