Upravljačka jedinica glavna je komponenta središnje procesorske jedinice (CPU) u računalima koja može usmjeravati operacije tijekom izvršavanja programa pomoću procesor /Računalo. Glavna funkcija upravljačke jedinice je dohvaćanje i izvršavanje uputa iz memorije računala. Od korisnika prima ulazne upute / informacije i pretvara ih u upravljački signali , koji se zatim daju CPU-u na daljnje izvršavanje. Uključen je kao dio Von Neumannove arhitekture koju je razvio John Neumann. Odgovorna je za davanje vremenskih signala i upravljanje signalima i usmjeravanje izvršenja programa od strane CPU-a. Uključen je kao interni dio CPU-a u moderna računala. Ovaj članak opisuje potpune informacije o upravljačkoj jedinici.

Što je upravljačka jedinica?

Komponenta koja prima ulazni signal / informaciju / uputu od korisnika i pretvara se u upravljačke signale za izvršavanje u CPU-u. On kontrolira i usmjerava glavnu memoriju, aritmetičku i logičku jedinicu (ALU), ulazne i izlazne uređaje, a također je odgovoran za upute koje se šalju na CPU računala. Dohvaća upute iz glavna memorija procesora i šalje se registru uputa procesora koji sadrži sadržaj registra.

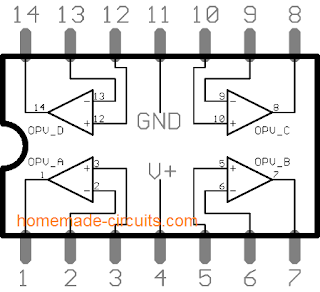

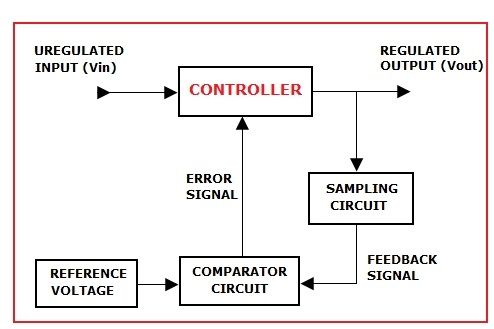

Blok dijagram upravljačke jedinice

Upravljačka jedinica pretvara ulaz u upravljačke signale, a zatim se šalje procesoru i usmjerava izvršavanje programa. Operacije koje je trebalo izvršiti usmjerava procesor na računalu. Uglavnom središnja procesorska jedinica (CPU) i Jedinica za grafičku obradu (GPU) zahtijeva upravljačku jedinicu kao unutarnji dio. Blok shema upravljačke jedinice prikazana je gore.

Sastavni dijelovi upravljačke jedinice

Sastavni dijelovi ove jedinice su upute registri , upravljački signali unutar CPU-a, upravljački signali prema / od sabirnice, upravljačka sabirnica, ulazne zastavice i signali sata.

Komponente Hardwired upravljačke jedinice su registar uputa (sadrži optički kod i polje adrese), mjerna jedinica, stanje upravljanja generator , matrica generiranja upravljačkog signala i dekoder instrukcija.

Komponente mikro programirane upravljačke jedinice su sljedeći generator adresa, kontrolni registar adresa, upravljačka memorija i registar kontrolnih podataka.

Funkcije

The funkcije upravljačke jedinice uključuju sljedeće.

- Usmjerava tok slijeda podataka između procesora i drugih uređaja.

- Može tumačiti upute i kontrolirati protok podataka u procesoru.

- Generira redoslijed upravljačkih signala iz primljenih uputa ili naredbi iz registra uputa.

- Odgovorna je za kontrolu izvršnih jedinica kao što su ALU, međuspremnici podataka i registri u CPU-u računala.

- Ima sposobnost dohvaćanja, dekodiranja, rukovanja izvršenjem i pohrane rezultata.

- Ne može obrađivati i pohranjivati podatke

- Za prijenos podataka komunicira s ulaznim i izlaznim uređajima i kontrolira sve jedinice računala.

Dizajn upravljačke jedinice

Dizajn se može izvesti pomoću dva vrste upravljačke jedinice koji uključuju sljedeće.

- Na temelju žičane mreže

- Mikroprogramirani (jednorazinski i dvorazinski)

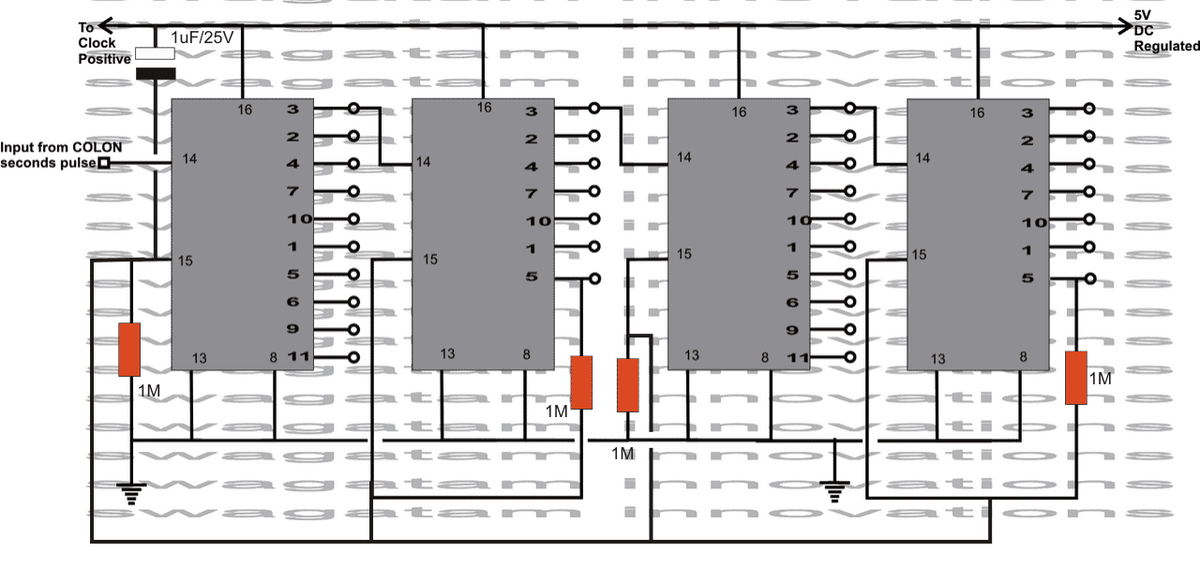

Hardverska upravljačka jedinica

Osnovni dizajn hardverske upravljačke jedinice prikazan je gore. U ovom tipu upravljački signali generiraju se posebnim hardverom logički sklop bez ikakve promjene u strukturi sklopa. U tom se slučaju generirani signal ne može modificirati za izvršavanje u procesoru.

Osnovni podaci operativnog koda (radni kod instrukcije šalje se dekoderu uputa na dekodiranje. Uputa dekoder je skup dekodera za dekodiranje različitih vrsta podataka u opcodeu. To rezultira izlaznim signalima koji sadrže vrijednosti aktivnih signala koji se daju kao ulaz u generator matrice za generiranje upravljačkih signala za izvršavanje programa od strane procesora računala.

Upravljačka jedinica temeljena na žičanom sustavu

Generator matrice pruža stanja upravljačke jedinice i signale koji izlaze iz procesora (signali prekida). Matrica je građena kao programabilni logički niz . Kontrolni signali koje generira matrični generator daju se kao ulaz u sljedeću matricu generatora i kombiniraju se s vremenskim signalima vremenske jedinice koja sadrži pravokutne uzorke.

Za dohvaćanje nove instrukcije, upravljačka jedinica pretvara se u početnu fazu za izvršavanje nove instrukcije. Upravljačka jedinica ostaje u početnoj fazi ili prvoj fazi dok su vremenski signali, ulazni signali i stanja uputa računala nepromijenjeni. Promjena stanja upravljačke jedinice može se povećati ako dođe do promjene bilo kojeg od generiranih signala.

Kada se dogodi vanjski signal ili prekid, upravljačka jedinica prelazi u sljedeće stanje i izvodi obradu signala prekida. Zastave i stanja koriste se za odabir željenih stanja za izvođenje ciklusa izvršavanja naredbe.

U posljednjem stanju, upravljačka jedinica dohvaća sljedeću naredbu i šalje izlaz na programski brojač, zatim u registar memorijske adrese, u međuspremnik, a zatim u registar naredbi za čitanje upute. Konačno, ako je zadnja naredba (koju dohvaća upravljačka jedinica) krajnja, ona prelazi u radno stanje procesora i čeka dok korisnik ne usmjeri sljedeći program.

Mikroprogramirana upravljačka jedinica

U ovom tipu, kontrolno spremište služi za pohranu kontrolnih signala koji su kodirani tijekom izvršavanja programa. Kontrolni signal ne generira se odmah i dekodira jer mikroprogram sprema polje adrese u kontrolnom spremištu. Cijeli postupak je na jednoj razini.

Mikro-operacije se rade za izvršavanje mikro-uputa u programu. Blok dijagram mikro programirane upravljačke jedinice prikazan je gore. Iz dijagrama se adresa mikro-instrukcije dobiva iz registra adresa upravljačke memorije. Sve informacije o upravljačkoj jedinici trajno se pohranjuju u upravljačku memoriju koja se naziva ROM.

Mikroprogramirana upravljačka jedinica

Mikronaputak iz upravljačke memorije drži kontrolni registar. Budući da je mikro-uputa u obliku kontrolne riječi (sadrži binarne kontrolne vrijednosti) kojoj je potrebna jedna ili više mikro-operacija za obradu podataka.

Tijekom izvršavanja mikro-naredbi, sljedeći je generator adresa izračunao sljedeću adresu mikro-instrukcije, a zatim poslao u registar kontrolnih adresa da pročita sljedeću mikro-instrukciju.

Slijed mikro-operacija mikro-programa izvodi sljedeći generator adresa i djeluje kao mikroprogramski sekvencer za dobivanje adrese sekvence, tj. Očitavanje iz kontrolne memorije.

Verilog kod za upravljačku jedinicu

Verilog kôd za upravljačku jedinicu prikazan je u nastavku.

`uključuju' prj_definition.v '

modul CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATADR_RETR_RED

// Izlazni signali

// Izlazi za datoteku registra

izlaz [`DATA_INDEX_LIMIT: 0] RF_DATA_W

izlaz [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

izlaz RF_READ, RF_WRITE

// Izlazi za ALU

izlaz [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

izlaz [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Izlazi za memoriju

izlaz [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

izlaz MEM_READ, MEM_WRITE

// Ulazni signali

ulaz [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

ulaz NULA, CLK, RST

// Ulazni signal

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Državne mreže

žica [2: 0] proc_state

// sadrži vrijednost brojača programa, pohranjuje trenutnu uputu, registar pokazivača steka

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] stanje, sljedeće_država

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

uvijek @ (posedge CLK)

početi

ako (RST)

država<= RST

drugo

država<= next_state

kraj

uvijek @ (država)

početi

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

slučaj (država)

`PROC_FETCH: započni

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

kraj

`PROC_DECODE: započni

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

kraj

`PROC_EXE: započni

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

kraj

`PROC_MEM: započni

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

kraj

`PROC_WB: započni

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

kraj

završno slovo

kraj

završni modul

modul PROC_SM (STANJE, CLK, RST)

// popis ulaza

ulaz CLK, RST

// popis izlaza

izlaz [2: 0] STANJE

// popis unosa

ulaz CLK, RST

// izlazni popis

izlaz STATE

reg [2: 0] STANJE

reg [1: 0] država

reg [1: 0] sljedeća_država

reg PC_REG, INST_REG, SP_REF

`definirajte PROC_FETCH 3’h0

`definirajte PROC_DECODE 3’h1

`definirajte PROC_EXE 3’h2

`definirajte PROC_MEM 3’h3

`definirajte PROC_WB 3’h4

// pokretanje države

početni

početi

stanje = 2’bxx

next_state = `PROC_FETCH

kraj

// resetiranje rukovanja signalom

uvijek @ (posedge RST)

početi

stanje = `PROC_FETCH

next_state = `PROC_FETCH

kraj

uvijek @ (posedge CLK)

početi

stanje = next_state

kraj

uvijek @ (država)

početi

if (stanje === `PROC_FETCH)

početi

next_state = `PROC_DECODE

upute za ispis (INST_REG)

kraj

if (stanje === `PROC_DECODE)

početi

next_state = `PROC_EXE

kraj

if (stanje === `PROC_EXE)

početi

next_state = `PROC_MEM

upute za ispis (SP_REF)

kraj

if (stanje === `PROC_MEM)

početi

next_state = `PROC_WB

kraj

if (stanje === `PROC_WB)

početi

next_state = `PROC_FETCH

upute za ispis (PC_REG)

kraj

kraj

zadatak print_instruction

ulaz [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] optički kod

reg [4: 0] rs

reg [4: 0] st

reg. [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] neposredna reg [25: 0] adresa

početi

// raščlaniti uputu

// R-tip

{opcode, rs, rt, rd, shamt, funct} = inst

// I-type

{opcode, rs, rt, neposredni} = inst

// J-tip

{opcode, adresa} = inst

$ write (“@% 6dns -> [0X% 08h]“, $ vrijeme, inst)

slučaj (opcode) // R-Type

6'h00: početak

slučaj (funkcija)

6’h20: $ write (“dodaj r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h22: $ write (“sub r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2c: $ write (“mul r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h24: $ write (“i r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h25: $ write (“ili r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h27: $ write (“niti r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2a: $ write (“slt r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h00: $ write (“sll r [% 02d],% 2d, r [% 02d]“, rs, shamt, rd)

6’h02: $ write (“srl r [% 02d], 0X% 02h, r [% 02d]”, rs, shamt, rd)

6’h08: $ write (“jr r [% 02d]”, rs)

zadano: $ write (“”)

završno slovo

kraj

// I-type

6’h08: $ write (“addi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h1d: $ write (“muli r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h0c: $ write (“andi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h0d: $ write (“ori r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h0f: $ write (“lui r [% 02d], 0X% 04h“, rt, odmah)

6’h0a: $ write (“slti r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h04: $ write (“beq r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h05: $ write (“bne r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h23: $ write (“lw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

6’h2b: $ write (“sw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, odmah)

// J-tip

6’h02: $ write (“jmp 0X% 07h”, adresa)

6’h03: $ write (“jal 0X% 07h”, adresa)

6’h1b: $ write (“push”)

6’h1c: $ write (“pop”)

zadano: $ write (“”)

završno slovo

$ write (“ n”)

kraj

krajnji zadatak

krajnji modul

Najčešća pitanja

1). Koji je rad upravljačke jedinice?

Rad upravljačke jedinice je usmjeravanje protoka podataka ili uputa za izvršenje od strane procesora računala. On kontrolira, upravlja i koordinira glavnu memoriju, ALU, registre, ulazne i izlazne jedinice. Dohvaća upute i generira kontrolne signale za izvršenje.

2). Što je kontrolna memorija?

Kontrolna memorija obično je RAM ili ROM za pohranu adrese i podataka kontrolnog registra.

3). Što je Wilkes upravljačka jedinica?

Sekvencijalni i kombinacijski krugovi tvrdo ožičene upravljačke jedinice zamjenjuju se Wilkesovom upravljačkom jedinicom. Koristi jedinicu za pohranu za pohranu nizova uputa mikro-programa.

4). Što je ožičena upravljačka jedinica?

Ožičena upravljačka jedinica generira upravljačke signale mijenjajući se iz jednog stanja u drugo u svakom impulsu takta bez ikakvih fizičkih promjena u krugu. Generiranje upravljačkih signala ovisi o registru uputa, dekoderu i signalima prekida.

5). Što je kontrolna memorija?

Podaci upravljačke jedinice ili podaci privremeno su ili trajno pohranjeni u upravljačku memoriju.

Kontrolna memorija je dvije vrste. To su memorija s slučajnim pristupom (RAM) i memorija samo za čitanje (ROM).

Dakle, ovdje se radi o definiciji, komponentama, dizajnu, dijagramu, funkcijama i vrste upravljačke jedinice . Evo pitanja za vas: 'Koja je svrha registra kontrolnih adresa?'