Ispravno izračunati postupak uključivanja MOSFET-a osigurava da je uređaj UKLJUČEN s optimalnom učinkovitošću.

Dok ste dizajnirali MOSFET sklopove, možda ste se pitali koji je ispravan način UKLJUČIVANJA MOSFET-a? Ili jednostavno koji je minimalni napon koji treba primijeniti na vrata / izvor uređaja kako bi se savršeno uključio?

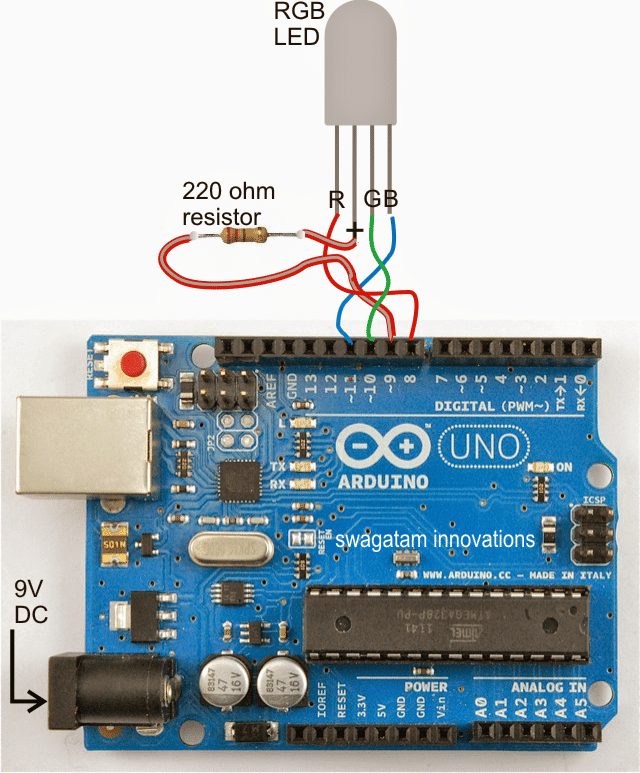

Iako za mnoge digitalne sustave to možda ne predstavlja problem, 5V sustavi poput DSP-a, FPGA-a i Arduinosa zahtijevaju jačanje njihovih rezultata za optimalne uvjete prebacivanja za spojeni MOSFET.

I u tim situacijama dizajner započinje sagledavanje specifikacija MOSFET-a kako bi dobio podatke o pragu napona. Dizajner pretpostavlja da bi se MOSFET uključio i promijenio stanje kada se pređe ovaj prag.

Međutim, ovo možda nije tako jednostavno kao što se čini.

Što je prag napona VGS (th)

Prije svega moramo shvatiti da je prag napona, označen kao VGS (th)nije za dizajnere sklopova da brinu.

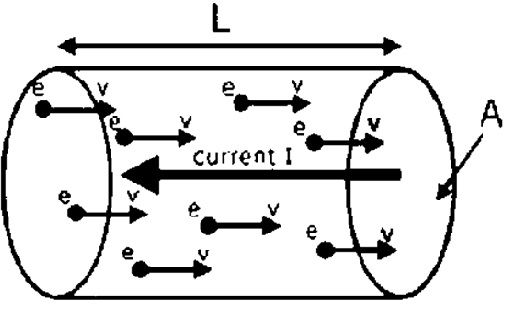

Točnije, napon na vratima uzrokuje da odvodna struja MOSFET-a prijeđe graničnu razinu od 250 μA, a to se ispituje u uvjetima koji u praksi nikad ne bi mogli proći u praksi.

Tijekom određenih analiza koristi se konstantna 5V za gore spomenuta ispitivanja uređaja. Ali ovaj se test obično provodi s međusklopom i odvodom uređaja koji su međusobno spojeni ili u kratkom spoju. Te podatke možete lako dobiti u samom tehničkom listu, tako da u ovom testu nema ništa tajanstveno.

Gornja tablica prikazuje granične vrijednosti i relevantne uvjete ispitivanja za primjer MOSFET-a.

Za željenu primjenu dizajner bi mogao biti zabrinut zbog zastrašujuće situacije poznate kao 'inducirani' napon na vratima, što može biti ozbiljan problem, na primjer u MOSFET-u male donje strane sinkroni pretvarač dolara .

Kao što je ranije spomenuto, i ovdje moramo shvatiti da prelazak praga VGS (th)razina možda neće prisiliti uređaj da uđe u stanje proboja. Ova razina zapravo govori dizajneru u vezi s pragom na kojem MOSFET tek počinje UKLJUČAVATI i nije situacija u kojoj stvari jednostavno završavaju.

Može biti preporučljivo da se, dok je MOSFET u isključenom stanju, napon na vratima održava ispod VGS (th)razini, kako bi se spriječilo curenje struje. No dok se UKLJUČUJE, ovaj se parametar može jednostavno zanemariti.

Karakteristična krivulja prijenosa

Pronaći ćete još jedan dijagram krivulje s imenom karakteristike prijenosa u MOSFET listovima podataka koji objašnjavaju njegovo UKLJUČENO ponašanje kao odgovor na povećanje napona vrata.

Točnije ovo može biti više povezano s analizom varijacija struje s obzirom na napon vrata i temperaturu kućišta uređaja. U ovoj analizi VDSse održava na fiksnoj, ali visokoj razini, oko 15 V, što se možda neće otkriti u specifikacijama tablice.

Ako se referiramo na krivulju kao što je gore prikazano, shvatit ćemo da za odvodnu struju od 20 Amp napon od 3,2 V od izvora do izvora možda neće biti dovoljan.

Kombinacija bi rezultirala VDS od 10 V, obično s rasipanjem od 200 W.

Podaci krivulje prijenosa mogu biti korisni za MOSFET-ove koji rade u linearnom rasponu, međutim podaci krivulje mogu imati manje značaja za MOSFET-ove u komutacijskim aplikacijama.

Izlazne karakteristike

Krivulja koja otkriva stvarne podatke o stanju potpuno uključenog MOSFET-a poznata je kao krivulja izlaza kako je prikazano dolje:

Ovdje, za različite razine VGSpad MOSFET-a prema naprijed mjeri se kao funkcija struje. Inženjeri uređaja koriste ove podatke krivulje kako bi potvrdili optimalnu razinu napona vrata.

Za svaku razinu napona na vratima koji osigurava potpuno uključivanje MOSFET-a [RDS (uključeno)], dobivamo niz padova napona (VGS) preko odvoda do izvora koji ima strogo linearni odziv s odvodnom strujom. Raspon započinje od nule pa naviše.

Za niže napone na vratima (VGS), kada je odvodna struja povećana, nalazimo da krivulja gubi linearni odziv, krećući se kroz 'koljeno', a zatim ide ravno.

Gore navedeni detalji krivulje pružaju nam cjelovite izlazne karakteristike za raspon napona na vratima od 2,5 V do 3,6 V.

Korisnici MOSFET-a to obično mogu smatrati linearnom funkcijom. Međutim, za razliku od inženjera uređaja, možda će radije obratiti više pažnje na sivo područje grafikona koje sugerira trenutno područje zasićenja za primijenjeni napon vrata.

Otkriva trenutne podatke koji su dodirnuli točku zasićenja ili granicu zasićenja. U ovom trenutku, ako je VDSAko se poveća, rezultirat će graničnim porastom struje, ali mali porast odvodne struje može dovesti do puno većeg VDS.

Za povećane razine napona na vratima, koje omogućuju MOSFET-u da se u potpunosti UKLJUČI, zeleno zasjenjeno područje pokazat će nam radnu točku procesa, naznačenu kao otporno (ili omsko) područje.

Napominjemo da ovdje krivulje prikazuju samo tipične vrijednosti i ne uključuju nikakve minimalne ili maksimalne granice.

Dok radi na nižim temperaturama okoline, uređaj će zahtijevati veći napon na vratima da ostane u otpornom području, što može ići prema gore brzinom od 0,3% / ° C.

Što je MOSFET RDS (uključen)

Kad se inženjeri uređaja moraju susresti s izlaznim karakteristikama MOSFET-a, u osnovi će htjeti naučiti o R-uDS (uključeno)uređaja s obzirom na određene radne uvjete.

Općenito, ovo može biti kombinacija VGSi jaDSpreko područja gdje je krivulja odstupila od ravne crte u dio označen sivom sjenom.

Uzimajući u obzir prethodno raspravljeni primjer, napon vrata od 3,1 V s početnom strujom od 10 ampera, inženjeri će znati da RDS (uključeno)težit će biti veća od procijenjene vrijednosti. Nakon ovoga, očekujemo li da će proizvođač MOSFET-a pružiti približne podatke u vezi s tim?

S obje veličine VDSi jaDSlako dostupna u krivulji može postati previše primamljiva i često joj se predaje da bi se dvije veličine podijelile na rezultantu RDS (uključeno).

Međutim, nažalost, nemamo RDS (uključeno)za procjenu ovdje. Čini se da nije dostupan za spomenute situacije jer ni za jedan odjeljak teretni vod koji predstavlja otpor mora linearno prijeći ishodište.

Međutim, možda je moguće simulirati vod tereta u agregiranom obliku poput nelinearnog otpora.

To će minimalno jamčiti da se svako razumijevanje praktičnog rada održava u ishodištu (0, 0).

Karakteristike krivulje punjenja vrata

Podaci o krivulji napunjenosti vrata zapravo nam daju stvarni nagovještaj u pogledu specifikacija UKLJUČIVANJA MOSFET-a, kao što je prikazano na donjoj slici :

Iako je gornja krivulja standardno uključivanje u sve MOSFET-ove podatkovne listove, osnovne indikacije korisnik MOSFET-a rijetko shvaća.

Štoviše, moderni napredak u MOSFET rasporedima, poput rova i zaštićenih vrata, zahtijeva revidirano adresiranje podataka.

Na primjer, specifikacija nazvana 'punjenje vrata' može izgledati pomalo zavaravajuća.

Linearni i podijeljeni dijelovi krivulje ne izgledaju poput napona koji puni kondenzator, bez obzira na to koliku nelinearnu vrijednost može pokazivati.

Točnije, krivulja napunjenosti vrata označava povezane podatke dvaju neparalelnih kondenzatora, koji imaju različite veličine i nose različite razine napona.

U teoriji, funkcionalni kapacitet kao što je svjedočio s terminala MOSFET vrata definiran je jednadžbom:

Cbr= Cgs+ Cgd

gdje je Cbr= kapacitet kapije, Cgs= kapacitet izvora izvora, Cgd= kapacitet odvoda vrata

Iako se može mjeriti ovu jedinicu i navesti u tablicama podataka prilično jednostavno, mora se primijetiti da pojam Cbrzapravo nije stvarni kapacitet.

Možda je potpuno pogrešno misliti da je MOSFET UKLJUČEN samo naponom koji je primijenjen na 'kapacitivnosti vrata'br'.

Kao što je naznačeno na gornjoj slici, neposredno prije uključivanja MOFET-a, kapacitet ulaza nema punjenja, već kapacitet na odvodu Cgdposjeduje negativni naboj koji treba eliminirati.

Oba ova kapaciteta imaju nelinearnu prirodu i njihove vrijednosti uvelike variraju kako variraju primijenjeni naponi.

Stoga je važno napomenuti da pohranjeni naboji MOSFET-a određuju njegove preklopne karakteristike, a ne vrijednost kapacitivnosti za određenu naponsku razinu.

Budući da dva elementa kapacitivnosti koji čine Cbrimaju različite fizičke atribute, obično se pune različitim naponskim razinama, što zahtijeva da postupak UKLJUČIVANJA MOSFET-a također prođe kroz dvije faze.

Precizni redoslijed može biti različit za otporne i induktivne primjene, ali obično je većina praktičnih opterećenja vrlo induktivna, a postupak se može simulirati kako je prikazano na sljedećoj slici:

Redoslijed vremena punjenja ulaza

Slijed vremenskog slijeda napunjenosti vrata MOSFET-a može se proučiti na donjem dijagramu:

To se može razumjeti sa sljedećim objašnjenjem:

- T0 - T1: Cgsnaboja od nule do VGS (th)... VDSili jaDSne prolazi kroz bilo kakve promjene.

- T1-T2, struja počinje rasti u MOSFET-u kao odgovor na rastući napon vrata od VGS (th)do napona platoa Vgp.

- Ovdje se IDS povećava i doseže struju punog opterećenja od 0 V, iako je VDSostaje nepromijenjen i konstantan. Pridruženi naboj nastaje kroz integral Cgsod 0 V do Vgp, i Qgsdane u tablicama.

- T2 - T3: Promatrajte ravno područje između T2 i T3, zove se Millerova visoravan.

- Prije prekidača ON, Cgdpuni i drži do napona napajanja VU, dok jaDSdoseže vršnu vrijednost I (opterećenje) na T2.

- Vrijeme između razdoblja T2 i T3, negativni naboj (VU- Vgp) pretvara se u pozitivni naboj s obzirom na napon platoa Vgp.

- To se također može vizualizirati kao pad odvodnog napona s VUna gotovo gotovo nulu.

- Uključeni naboj jednak je oko Cgdintegral od 0 do Vu, koji je prikazan kao Qgdu tablicama podataka.

- Tijekom T3 - T4, napon na vratima se penje od Vgpdo VGS, i ovdje teško nalazimo bilo kakvu promjenu za VDSi jaDS, ali efektivni RDS (uključeno)lagano pada s porastom napona na vratima. Na nekom naponskom nivou iznad Vgp, pruža proizvođačima dovoljno samopouzdanja da fiksiraju gornju granicu efektivnog RDS (uključeno).

Za induktivna opterećenja

Porast struje u MOSFET kanalu zbog induktivnog opterećenja treba završiti prije nego što napon počne padati.

Na početku visoravni, MOSFET je u stanju ISKLJUČENO, u prisutnosti velike struje i napona preko odvoda do izvora.

Između vremena T2 i T3, naboj Qgdprimjenjuje se na ulaz MOSFET-a, pri čemu se MOSFET-karakteristika na kraju transformira iz konstantne struje u način konstantnog otpora.

Kada se dogodi gornji prijelaz, nema zamjetne promjene napona V na vratimagpodvija se.

To je razlog zašto nikad nije pametno povezati postupak uključivanja MOSFET-a s bilo kojom određenom razinom napona na vratima.

Isto može vrijediti i za postupak ISKLJUČIVANJA, koji zahtijeva da se ista dva naboja (o kojima je ranije bilo riječi) eliminiraju s vrata MOSFET-a suprotnim redoslijedom.

MOSFET brzina prebacivanja

Dok je Qgsplus Qgdzajedno osigurava da će se MOSFET potpuno uključiti, ne govori nam o tome koliko će se brzo to dogoditi.

Koliko će se brzo prebaciti struja ili napon, odlučuje brzina kojom se nabojni elementi na vratima primjenjuju ili uklanjaju. To se također naziva strujom pogonskog sklopa.

Iako brza brzina porasta i pada osigurava niže preklopne gubitke u MOSFET-ovima, oni također mogu dovesti do komplikacija na razini sustava povezanih s povećanim vršnim naponima, oscilacijama i elektromagnetskim smetnjama, posebno tijekom isključenja induktivnog opterećenja.

Linearno padajući napon prikazan na gornjoj slici 7 uspijeva uzeti konstantnu vrijednost Cgd, što se MOSFET-ovima u praktičnoj primjeni teško može dogoditi.

Točnije, punjenje odvoda vrata Cgdza visokonaponski super-spoj MOSFET poput SiHF35N60E pokazuje značajno visok linearni odziv, kao što se može vidjeti na sljedećoj slici:

Raspon varijacija koji postoji u vrijednosti Crss(obrnuti prijenos) je više od 200: 1 unutar početnih 100 V. Zbog toga stvarno vrijeme pada napona prema krivulji punjenja vrata više izgleda poput isprekidane crte prikazane crvenom bojom na slici 7.

Pri višim naponima, porast i pad naboja, zajedno s njihovim ekvivalentnim vrijednostima dV / dt, više ovise o vrijednosti Crss, umjesto integrala cijele krivulje označene kao Qgd.

Kada korisnici žele usporediti MOSFET specifikacije u različitim dizajnerskim okruženjima, trebali bi shvatiti da MOSFET s pola Qgdvrijednost neće nužno imati dvostruko bržu brzinu prebacivanja ili 50% manje prebacivanje gubitaka.

To je zato što, prema Cgdkrivulje i njezine veličine pri višim naponima, možda je sasvim moguće da MOSFET ima nizak Qgd u podatkovnom listu, ali bez ikakvog povećanja brzine prebacivanja.

Rezimirajući

U stvarnoj provedbi, UKLJUČIVANJE MOSFET-a događa se kroz niz procesa, a ne s unaprijed određenim parametrom.

Dizajneri sklopova moraju prestati zamišljati da VGS (th), ili se razine napona mogu koristiti kao napon na vratima za prebacivanje MOSFET izlaza s visokog na niski RDS (uključeno).

Možda je uzaludno razmišljati o tome da imam RDS (uključeno)ispod ili iznad određene razine napona na vratima, jer razina napona na vratima suštinski ne odlučuje o UKLJUČIVANJU MOSFET-a. Umjesto da su optužbe Qgsi Qgduveden u MOSFET koji izvršava posao.

Možda ćete pronaći napon na vratima kako raste iznad VGS (th)i Vgptijekom postupka punjenja / pražnjenja, ali oni nisu toliko važni.

Isto tako, koliko brzo se današnji MOSFET može UKLJUČITI ili ISKLJUČITI može biti složena funkcija Q-agsili Qgd.

Za procjenu brzina prebacivanja MOSFET-a, posebno naprednih MOSFET-ova, dizajner mora proći sveobuhvatnu studiju u vezi s krivuljom punjenja vrata i karakteristikom kapacitivnosti uređaja.

Referenca: https://www.vishay.com/

Prethodno: Karakteristike prijenosa Dalje: TL494 tablica podataka, pinout, aplikacijski krugovi