Skup instrukcija ili arhitektura skupa instrukcija je struktura računala koja računalu daje naredbe za vođenje računala za obradu podataka. Skup uputa sastoji se od uputa, načina adresiranja, izvornih vrsta podataka, registara, prekida, rukovanja iznimkama i arhitekture memorije. Skup uputa može se oponašati u softveru pomoću interpretera ili ugraditi u hardver procesora. Arhitektura skupa uputa može se smatrati granicom između softvera i hardvera. Klasifikacija mikrokontrolera a mikroprocesori se mogu izvoditi na temelju arhitekture skupa naredbi RISC i CISC.

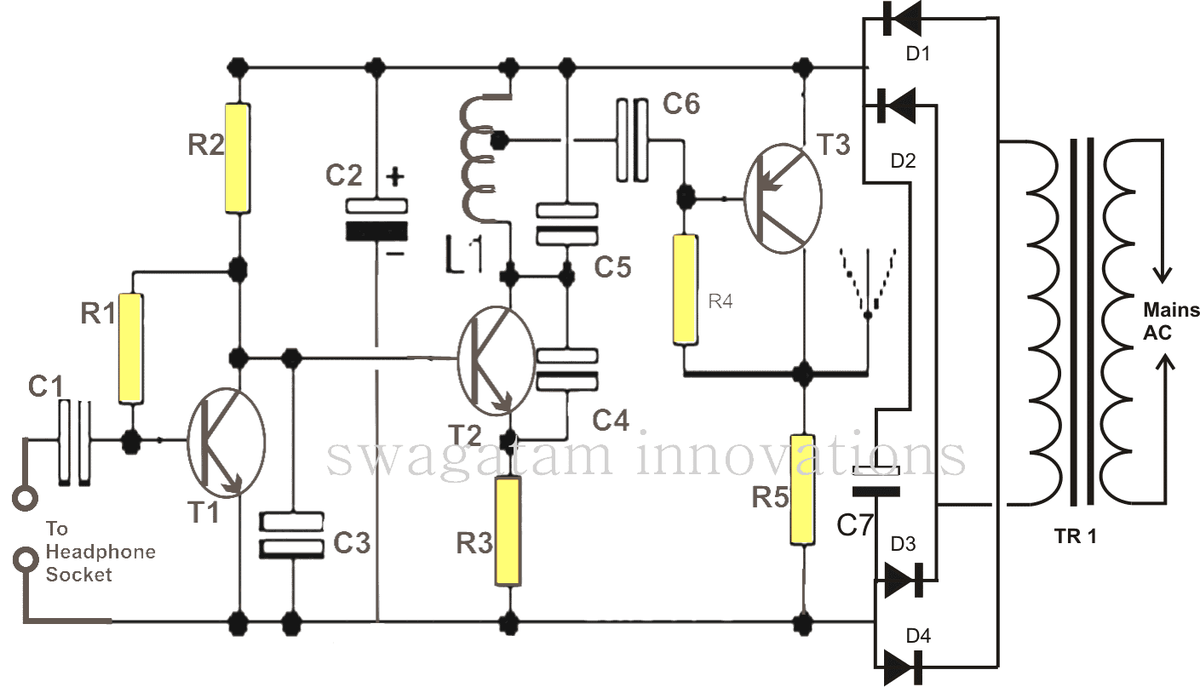

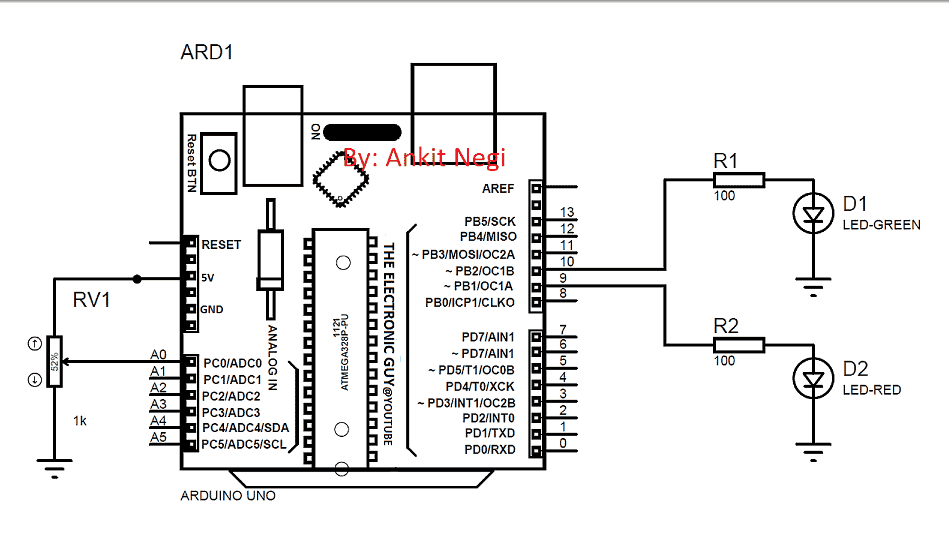

Set uputa procesora

Skup uputa specificira funkcionalnost procesora, uključujući radnje koje podržava procesor, mehanizme pohrane procesora i način sastavljanja programa u procesor.

Što su RISC i CISC?

The RISC i CISC može se proširiti na sljedeći način:

RISC predstavlja računalo sa smanjenim naputkom i

CISC predstavlja složeno računalo s uputama.

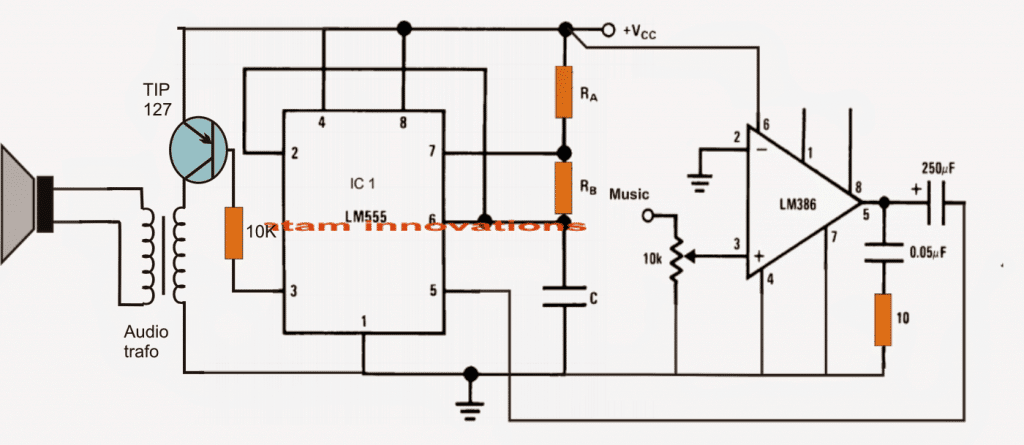

Arhitektura RISC (računalo s reduciranim uputama)

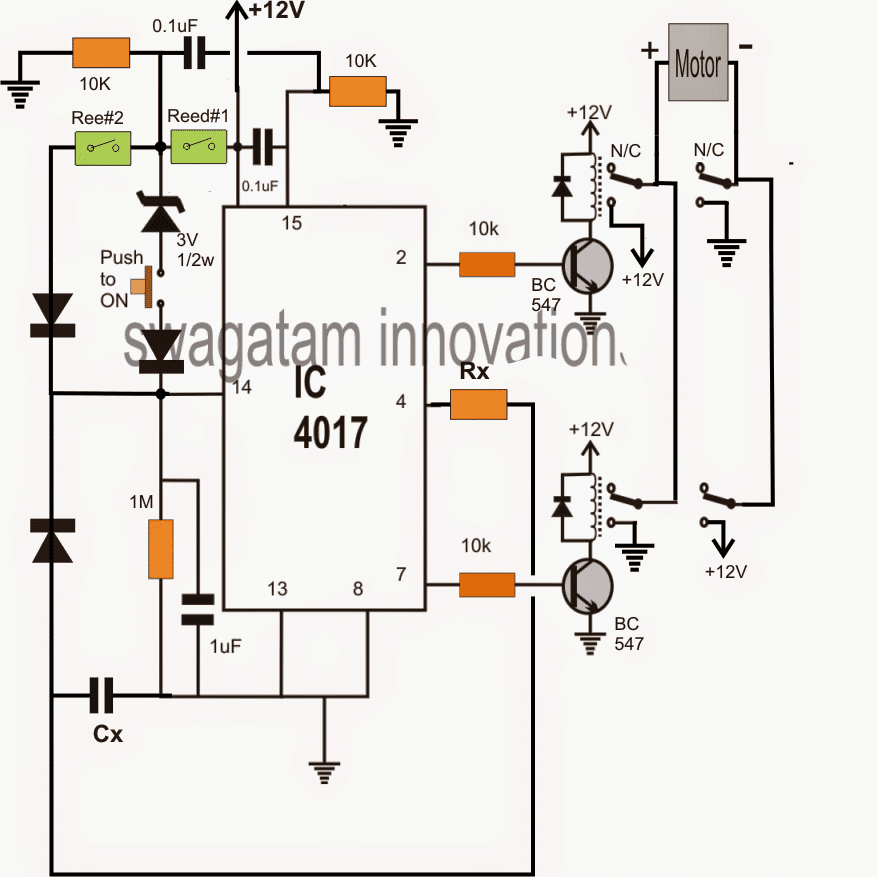

RISC arhitektura

The arhitektura mikrokontrolera koji koristi mali i visoko optimizirani skup uputa naziva se računalom sa smanjenim uputama ili jednostavno RISC. Naziva se i arhitekturom LOAD / STORE.

Krajem 1970-ih i početkom 1980-ih, RISC projekti prvenstveno su razvijani od Stanforda, UC-Berkleyja i IBM-a. John Coke iz IBM-ovog istraživačkog tima razvio je RISC smanjivanjem broja uputa potrebnih za bržu obradu izračunavanja od CISC-a. RISC arhitektura je brža, a čipovi potrebni za izradu RISC arhitekture također su jeftiniji u odnosu na CISC arhitekturu.

Tipične značajke RISC arhitekture

- Tehnika pipeliranja RISC-a izvršava istovremeno više dijelova ili faza uputa tako da je svaka uputa na CPU optimizirana. Dakle, RISC procesori imaju sat po uputi jednog ciklusa, a to se naziva Izvođenje jednog ciklusa.

- Optimizira uporaba registra s većim brojem registara u RISC-u i većim brojem interakcija unutar memorije može se spriječiti.

- Jednostavni načini adresiranja, čak i složeno adresiranje mogu se izvršiti pomoću aritmetike I / ILI logičke operacije .

- Pojednostavljuje dizajn kompajlera korištenjem identičnih registara opće namjene koji omogućuju upotrebu bilo kojeg registra u bilo kojem kontekstu.

- Za učinkovitu upotrebu registara i optimizaciju namjene cjevovoda potreban je smanjeni skup uputa.

- Smanjen je broj bitova koji se koriste za opcode.

- Općenito postoji 32 ili više registara u RISC-u.

Prednosti arhitekture RISC procesora

- Zbog malog skupa uputa RISC-a, kompajleri jezika na visokoj razini mogu proizvesti učinkovitiji kod.

- RISC omogućuje slobodu korištenja prostora na mikroprocesori zbog svoje jednostavnosti.

- Umjesto da koriste Stack, mnogi RISC procesori koriste registre za prosljeđivanje argumenata i zadržavanje lokalnih varijabli.

- RISC funkcije koriste samo nekoliko parametara, a RISC procesori ne mogu koristiti pozivne upute, pa stoga koriste upute fiksne duljine koje je lako provesti.

- Brzina operacije može se maksimizirati, a vrijeme izvršavanja može se smanjiti.

- Potreban je vrlo mali broj formata uputa (manje od četiri), nekoliko uputa (oko 150) i nekoliko načina adresiranja (manje od četiri).

Nedostaci arhitekture RISC procesora

- S povećanjem duljine uputa, povećava se složenost za izvršavanje RISC procesora zbog ciklusa znakova po naredbi.

- Izvedba RISC procesora najviše ovisi o prevoditelju ili programeru, jer znanje prevoditelja igra glavnu ulogu tijekom pretvaranja CISC koda u RISC kôd, pa stoga kvaliteta generiranog koda ovisi o prerađivaču.

- Tijekom reprogramiranja CISC koda na RISC kod, nazvan proširivanjem koda, povećat će se veličina. Kvaliteta ovog proširenja koda opet će ovisiti o prevoditelju, a također i o skupu uputa stroja.

- Predmemorija prve razine RISC procesora također je nedostatak RISC-a, u kojem ti procesori imaju velike memorijske predmemorije na samom čipu. Za hranjenje uputa trebaju vrlo brzi memorijski sustavi .

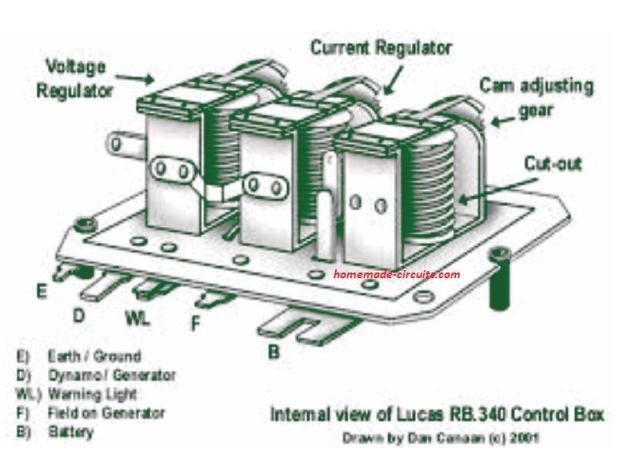

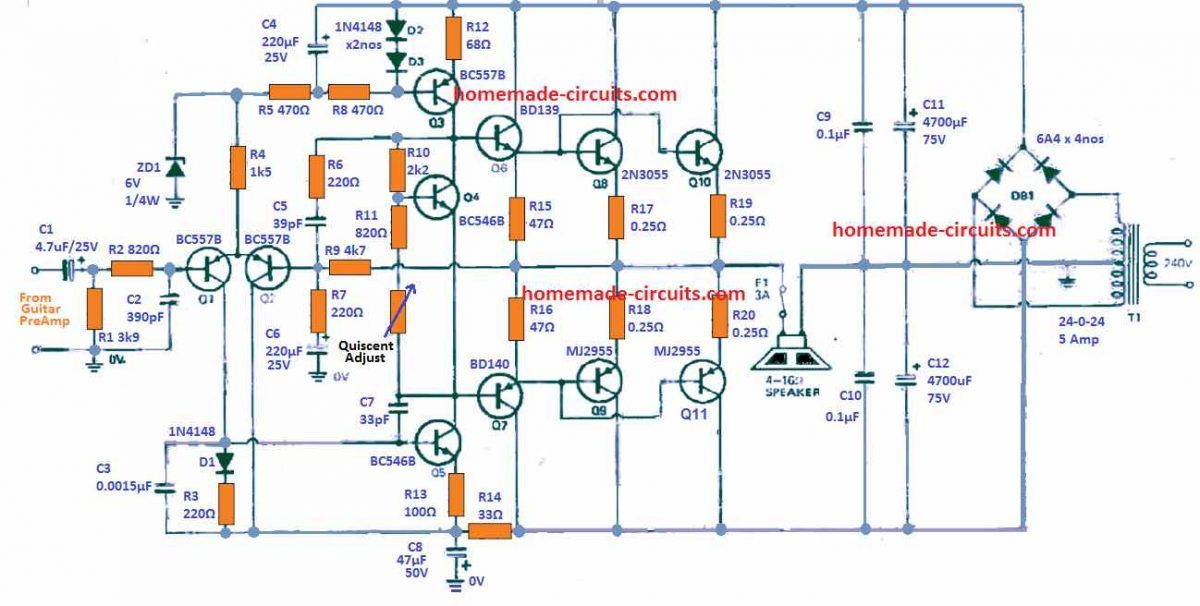

Arhitektura CISC (složeno računalo s instrukcijama)

Glavna namjera arhitekture CISC procesora je dovršiti zadatak korištenjem manjeg broja linija za montažu. U tu svrhu, procesor je izgrađen za izvršavanje niza operacija. Složena uputa također se naziva MULT, koja djeluje banke memorije računala izravno, a da kompajler ne izvršava funkcije spremanja i učitavanja.

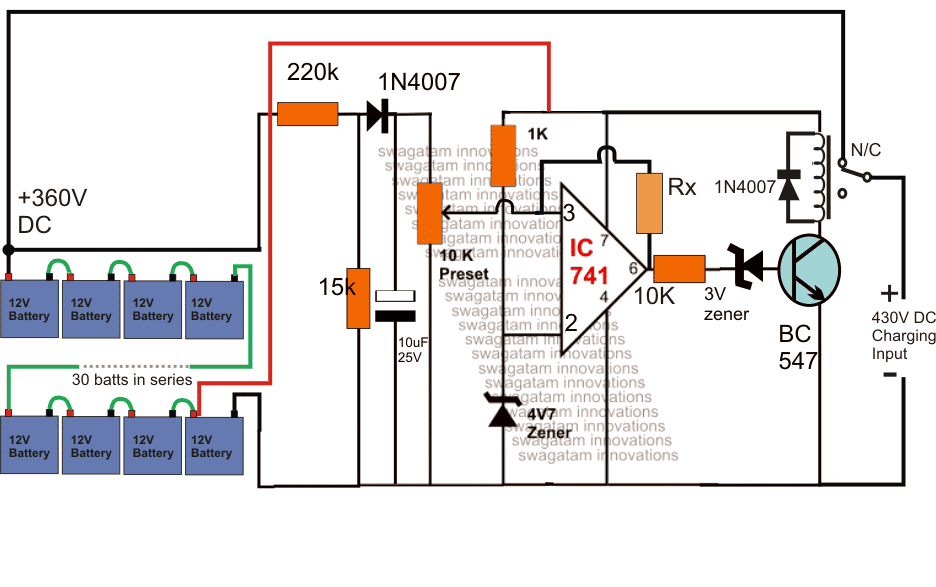

CISC arhitektura

Značajke CISC arhitekture

- Da bi pojednostavio arhitekturu računala, CISC podržava mikroprogramiranje.

- CISC ima veći broj unaprijed definiranih uputa što jezike na visokoj razini čini jednostavnim za dizajn i primjenu.

- CISC se sastoji od manjeg broja registara i većeg broja načina adresiranja, obično 5 do 20.

- CISC procesoru je potrebno različito vrijeme ciklusa za izvršavanje uputa - višečasovni ciklusi.

- Zbog složenog skupa uputa CISC-a, tehnika cjevovoda je vrlo teška.

- CISC se sastoji od većeg broja uputa, obično od 100 do 250.

- Posebne upute koriste se vrlo rijetko.

- Operandi u memoriji manipuliraju se uputama.

Prednosti CISC arhitekture

- Svaka se uputa strojnog jezika grupira u naredbu mikrokoda i izvršava u skladu s tim, a zatim se pohranjuje ugrađena u memoriju glavnog procesora, nazvana implementacijom mikrokoda.

- Kako je memorija mikrokoda brža od glavne memorije, set uputa za mikrokôd može se implementirati bez značajnog smanjenja brzine u odnosu na tvrdo žičnu implementaciju.

- Cjelokupnim novim setom uputa može se upravljati mijenjanjem dizajna mikro programa.

- CISC, broj uputa potrebnih za implementaciju programa može se smanjiti izgradnjom bogatih skupova naredbi, a može se učiniti i da učinkovitije koristi sporo glavnu memoriju.

- Zbog super skupa uputa koji se sastoji od svih ranijih uputa, ovo olakšava mikrokodiranje.

Nedostaci CISC-a

- Količina vremena sata koju uzimaju različite upute bit će različita - zbog toga - performanse stroja se usporavaju.

- Složenost skupa uputa i hardver čipa se povećavaju kako se svaka nova verzija procesora sastoji od podskupine ranijih generacija.

- Samo 20% postojećih uputa koristi se u tipičnom programskom događaju, iako postoji mnogo specijaliziranih uputa koje se čak i ne koriste često.

- Uvjetni kodovi postavljeni su uputama CISC-a kao nuspojava svake naredbe koja treba vremena za ovu postavku - i, kako sljedeća uputa mijenja bitove koda stanja, tako da prevodilac mora ispitati bitove koda stanja prije nego što se to dogodi.

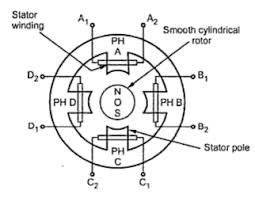

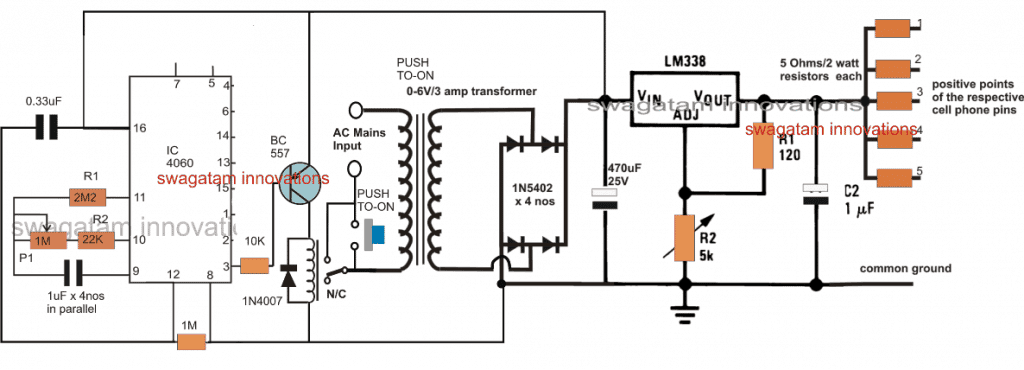

RISC vs. CISC

- Programer može spriječiti gubljenje ciklusa uklanjanjem nepotrebnog koda u RISC-u, ali, dok upotreba CISC koda dovodi do gubljenja ciklusa zbog neučinkovitosti CISC-a.

- U RISC-u je svaka instrukcija namijenjena izvođenju malog zadatka, tako da se za izvršavanje složenog zadatka koristi višestruka mala uputa zajedno, dok je za obavljanje istog zadatka pomoću CISC-a potrebno samo nekoliko uputa - jer je sposobno izvršiti složeni zadatak jer su upute slične kodu na visokom jeziku.

- CISC se obično koristi za računala, dok se RISC koristi za pametne telefone, tablete i druge elektroničke uređaje.

Sljedeća slika prikazuje više razlika između RISC-a i CISC-a

RISC vs. CISC

Stoga ovaj članak raspravlja o značajkama RISC i CISC arhitektura značajkama arhitekture RISC i CISC procesora, prednostima i nedostacima RISC i CISC te razlikama između RISC i CISC arhitektura s kratkom idejom. Za više informacija o RISC i CISC arhitekturama, objavite svoje komentare komentirajući dolje.

Foto bodovi:

- Set uputa Procesora od arstechnica

- RISC arhitektura lsi-natječaj

- RISC nasuprot CISC-u preusmjeravanje