Procesor MicroBlaze razvijen je 2002. godine kako bi integrirao nekoliko kompliciranih značajki kako bi zadovoljio nove, ali i rastuće zahtjeve tržišta. Dakle, MicroBlaze procesor je bitan element unutar niskobudžetnog portfelja Xilinxa kako bi se omogućio brži razvoj sustava koji sadrži Artix®-7 FPGA , Spartan®-6, Zynq®-7000 AP SoC. Ovaj procesor je izuzetno konfigurabilan, tako da se može koristiti kao ugrađeni procesor ili mikrokontroler unutar FPGA-a i također koristiti kao koprocesor u Zynq-7000 AP SoC-ovima koji se temelje na ARM Cortex-A9. Ovaj članak daje kratke informacije o MicroBlaze procesor – arhitektura i rad s aplikacijama.

Što je Microblaze procesor?

Meki mikroprocesor koji je dizajniran uglavnom za FPGA Xilinx poznat je kao MicroBlaze procesor. Ovaj procesor je jednostavno implementiran unutar memorije opće namjene i logičke strukture FPGA-a tvrtke Xilinx. Ovaj procesor sličan je DLX arhitekturi koja se temelji na RISC-u i ima fleksibilan sustav međusobnog povezivanja tako da podržava različite ugrađene aplikacije. Glavna ulazno-izlazna sabirnica i AXI interkonekt MicroBlazea je memorijski mapirana transakcijska sabirnica s glavnim i podređenim objektom.

MicroBlaze koristi namjensku LMB sabirnicu za pristup lokalnoj memoriji i pruža brzu pohranu na čipu. Mnogi dijelovi ovog procesora mogu biti konfigurirani od strane korisnika poput veličine predmemorije, dubine cjevovoda jedinice za upravljanje memorijom, ugrađenih perifernih uređaja i sučelja sabirnice.

Značajke Microblaze

The značajke Microblaza e uključuju sljedeće. Ima 32 registra opće namjene.

- Ima 32-bitne riječi instrukcija uključujući 2 načina adresiranja i 3 operanda.

- Adresna sabirnica je 32-bitna.

- Ima 3-stupanjski cjevovod ili 5-stupanjski cjevovod.

- ALU blok jedinica s mjenjačem.

- Harvardska arhitektura uključuje 32-bitnu podatkovnu i adresnu sabirnicu.

- Podatkovno sučelje & LMB ili instrukcija sabirnice lokalne memorije.

- AX14 i AX14 stream sučelja.

- Jedinica s pomičnim zarezom i jedinica za upravljanje memorijom.

- Podržava lockstep.

- Sučelje za otklanjanje pogrešaka i praćenje.

Microbaze arhitektura

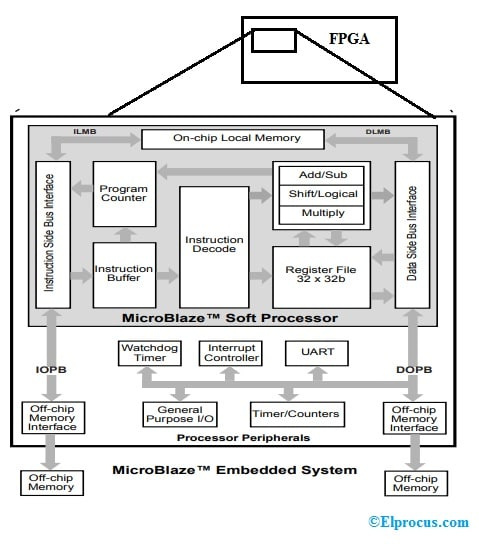

Dolje je prikazan blok dijagram MicroBlaze procesora. Ovaj MicroBlaze procesor iznimno je prilagodljiv i podržava više od 70 opcija dizajna. Ova arhitektura prikazuje stalne hardverske značajke kao i konfigurabilne opcije kao što su predmemorija instrukcija ili podataka, jedinica za upravljanje memorijom, jedinica s pomičnim zarezom itd.

An ugrađeni sustav sastavljen oko MicroBlaze procesora uglavnom uključuje MicroBlaze Soft Processor Core, lokalnu memoriju na čipu, standardne interkonekcije sabirnice i OPB periferne uređaje (periferna sabirnica na čipu). MicroBlaze procesorski sustav uglavnom se kreće od jezgre procesora s lokalnom memorijom do velikog sustava koji uključuje nekoliko MicroBlaze procesori , vanjska memorija i mnoge OPB periferije.

Meka jezgra procesora

Mekana procesorska jezgra MicroBlaze središnja je za MicroBlaze ugrađeni sustav. Ovo je vrlo brz i učinkovit 32-bitni RISC procesor koji ima sljedeće značajke.

- Skup instrukcija je ortogonalni.

- Odvojene sabirnice podataka i uputa.

- 32-bitni registri opće namjene.

- Ima dodatni potpuni 32-bitni bačvasti mjenjač.

- Ugrađena sučelja za brzi OCM ili memoriju na čipu & IBM-ov industrijski standard OPB (On-chip Peripheral Bus).

Implementacije unutar Virtex-II i kasnijih uređaja podržavaju višestruki hardver.

Lokalna memorija na čipu

Sinkrona memorija je lokalna memorija koja se uglavnom koristi za omogućavanje blok RAM-a na čipu.

Standardne sabirničke interkonekcije

Sučelja sabirnice na strani instrukcija i podataka uključuju sučelje za lokalnu memoriju koja se naziva LMB (Local Memory Bus) i sučelje za IBM-ovu perifernu sabirnicu na čipu. Dakle, možemo dizajnirati sustave koji se striktno drže harvardske arhitekture, inače, za dijeljenje resursa, možemo koristiti jedan OPB unutar kombinacije preko magistralnog arbitra.

Lokalna memorijska sabirnica daje osiguran ulaz u jednom ciklusu za blok RAM na čipu. Ovo je vrlo učinkovit, jednostavan protokol sabirnice s jednim glavnim i savršen je za povezivanje brze lokalne memorije. OPB ili On-chip Peripheral Bus je 32-bitna široka multi-master sabirnica koja je savršena za spajanje perifernih uređaja i vanjske memorije s jezgrom MicroBlaze procesora.

Periferne sabirnice na čipu

Hardverski sustav MicroBlaze upotpunjen je OPB periferijama za pružanje različitih funkcija kao što su Watchdog Timer ili Timebase, Timer opće namjene ili Brojači, IC (Interrupt Controller), različiti kontroleri kao što su SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, I/O opće namjene, UART 16450/550 i Ethernet 10/100 MAC. Osim toga, također možemo dodati i definirati periferne uređaje uglavnom za prilagođene funkcije, inače, sučelje za dizajn koji postoji u FPGA.

Set uputa za Microblaze

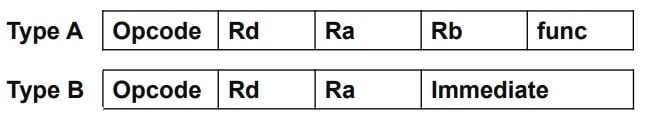

Microblaze skupovi instrukcija su aritmetika, logika, grananje, učitavanje/pohranjivanje i drugi. Veličina svih uputa je fiksna. Najviše 3-registra mogu se dati kao operandi. Microblaze uključuje dva formata uputa tipa A i tipa B koji su prikazani u nastavku.

Format instrukcije tipa A uglavnom se koristi za instrukcije registar-registar. Dakle, uključuje operacijski kod, jedno odredište i dva izvorna registra. Format instrukcije tipa B uglavnom se koristi za neposredne instrukcije registra koje uključuju operativni kod, jedno odredište i jedan izvorni registar.& 16-bitni neposredni izvor vrijednosti.

U gornja dva formata instrukcija, opcode je kod operacije, Rd je odredišni registar koji je kodiran s 5 bita, Ra & Rb su izvorni registri gdje je svaki kodiran s 5 bita, a Immediate je 16-bitna vrijednost.

Aritmetičke upute

U nastavku su dane aritmetičke upute tipa A i tipa B.

Tip A

|

DODAJTE Rd, Ra, Rb dodati |

Rd = Ra+Rb, pogođena zastavica Nošenja |

|

DODAJ K Rd, Ra, Rb Dodaj i nastavi nositi |

Rd = Ra+Rb, Carry zastavica nije pogođena |

| RSUB Rd, Ra, Rb Obrnuto oduzimanje |

Rd = R-Rb, Carry zastavica nije pogođena |

Tip B

|

DODAJ I Rd, Ra, Imm dodati odmah |

Rd = Ra+signExtend32 (Imm) |

|

DODAJTE IK Rd, Ra, Imm dodati odmah i nastaviti nositi |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm obrnuto oduzimanje s neposrednim |

Rd = Ra+ signExtend32 (Imm) -Ra |

| SRA Rd, Ra aritmetički pomak udesno |

Rd = (Ra>>1) |

Logičke upute

U nastavku su dane logičke upute tipa A i tipa B.

Tip A

|

ILI Rd, Ra, Rb Logično ili |

Rd = Ra| Rb |

|

I Rd,Ra,Rb Logičan dodatak |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Logotički xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logično i ne |

Rd = Ra & (Rb) |

Tip B

|

ORI Rd, Ra, Imm logički ILI s neposrednim |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm logično I s neposrednim |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logički XOR s neposrednim |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logično A NE odmah |

Rd = Ra & (signExtend32 (Imm)) |

Upute za podružnice - bezuvjetne

Izmijenite registar programskog brojača

| BRID Imm podružnica immediate s neposrednim kašnjenjem |

PC = PC+ signExtend32 (Imm) dopustiti izvođenje odgođenog utora |

| BRLID Rd, Imm grananje i veza odmah s trenutačnom odgodom (poziv funkcije) |

Rd = PC PC = PC+& signExtend32 (Imm) dopustiti izvođenje odgođenog utora |

| RTSD Ra, Imm povratak iz potprograma |

PC = Ra + signExtend32 (Imm) dopustiti izvođenje odgođenog utora |

| RTID Ra, Imm povratak iz prekida |

PC = Ra + signExtend32 (Imm) dopustiti izvođenje odgođenog utora set interrupt enable u MSR |

Upute za grane - bezuvjetne1

Promijenite registar programskog brojača kada je uvjet zadovoljen

| BEQI Ra, Imm grana ako je jednaka |

PC = PC+ signExtend32 (Imm) Ako je Ra = = 0 |

| MASH Ra, Imm grana ako nije jednaka |

Rd = PC PC = PC+& signExtend32 (Imm) Ako Ra! = 0 |

Upute za grane- bezuvjetne2

Promijenite registar programskog brojača kada je uvjet zadovoljen

| BLTI Ra, Imm grana ako je niža od |

PC = PC+ signExtend32 (Imm) Ako je Ra < 0 |

| BLEI Ra, Imm grana ako je niža jednaka |

Rd = PC PC = PC+& signExtend32 (Imm) Ako je Ra!< = 0 |

| BGTI Ra, Imm grana ako je veća od |

PC = PC+ signExtend32 (Imm) Ako je Ra!> 0 |

| BGEI Ra, Imm grana ako je veće jednako |

PC = PC+signExtend32 (Imm) Ako je Ra!>= 0 |

Upute za učitavanje/spremanje - tip A

| LW Rd, Ra, Rb Učitaj riječ |

Adresa = Ra+Rb Rd = *Adresa |

| JZ Rd, Ra, Rb Spremi riječ |

Adresa – Ra+Rb *Adresa = Rd |

Tip B

| LWI Rd, Ra, Imn Učitaj riječ odmah |

Adresa = Ra + signExtend32 (Imm) Rd = *Adresa |

| SW Rd, Ra, Imm Spremi riječ odmah |

Adresa = Ra + signExtend32 (Imm) *Adresa = Rd |

Ostale upute

| IMM, Imm neposredna |

Proširite Imm prethodne instrukcije tipa B na 32 bita. |

| MFS Rd, Sa Premjestiti iz registra posebne namjene |

Rd = Sa Sa- registar posebne namjene, izvorni operand

|

| MTS SD, Ra Premjestiti u registar posebne namjene |

Sd = Ra Sd – registar posebne namjene, odredišni operand |

Registri

Arhitektura MicroBlaze procesora potpuno je ortogonalna što uključuje 32-bitne registre opće namjene i 32-bitne registre posebne namjene poput programskog brojača i registra statusa stroja.

Arhitektura cjevovoda

MicroBlaze koristi 3-stupanjsku arhitekturu cjevovoda uključujući dohvaćanje, dekodiranje i potpune faze. Automatski se unutar hardvera određuje prosljeđivanje podataka, grananje i zastoj cjevovoda.

Učitaj ili pohrani arhitekturu

MicroBlaze podržava memoriju u tri veličine podataka 8 bita (Byte), 16 bita (Halfword) i 32 bita (Word). Dakle, pristupi memoriji uvijek su usklađeni s veličinom podataka. Ovo je Big-Endian procesor koji koristi adresu Big-Endian adrese kao i konvencije označavanja nakon pristupa memoriji.

Prekidi

Nakon što se dogodi prekid, tada će ovaj procesor prekinuti trenutno izvršenje kako bi upravljao zahtjevom za prekid kroz grananje na adresu vektora prekida i pohranio adresu instrukcije koja se treba izvršiti. Ovaj će procesor zaustaviti buduće prekide brisanjem oznake IE (Interrupt Enable) unutar MSR (Machine Status Register).

Kako Microblaze djeluje?

Procesor MicroBlaze podržava 32-bitnu širinu sabirnice, a ova procesorska jezgra je motor temeljen na RISC-u koji uključuje datoteku registra temeljenu na 32-bitnom LUT RAM-u putem zasebnih uputa za pristup memoriji i podacima.

Ovaj procesor jednostavno podržava i BlockRAM na čipu i vanjsku memoriju. Slično IBM PowerPC-u; svi periferni uređaji koriste sličnu sabirnicu CoreConnect OPB; periferne jedinice procesora dobro su usklađene s PowerPC-om na Virtex-II Pro.

MicroBlaze procesor pruža potpunu fleksibilnost za odabir kombinacije značajki memorije, perifernih uređaja i sučelja koje će vam pružiti precizan sustav koji vam je potreban na jednom FPGA uz manje troškove.

Razlika C/W Microblaze u odnosu na Risc-V

The razlika između MicroBlaze i RISC v uključuju sljedeće.

|

Microblaze |

Risc-V |

| To je meka mikroprocesorska jezgra uglavnom dizajnirana za Xilinx FPGA.

|

RISC-V je arhitektura skupa instrukcija ukorijenjena u RISC principima.

|

| Koristi Harvard RISC arhitekturu. | Koristi arhitekturu skupa instrukcija. |

| Njegova licenca je vlasnička (Xilinx) | Njegova licenca je otvorenog koda. |

| Dubina cjevovoda je 3 ili 5. | Dubina cjevovoda je 5. |

| Njegova izvedba je 280 DMIPs. | Njegova izvedba je 250 DMIPs. |

| Brzina mu je 235 MHz. | Brzina mu je 250 MHz. |

| Ima 1027 LUT-ova. | Ima 4125 LUT-ova. |

| Implementacija korištene tehnologije je Xilinx FPGA. | Implementacija korištene tehnologije je FPGA/ASIC. |

Microblaze prednosti

The prednosti MicroBlaze-a uključuju sljedeće.

- Ekonomičan je.

- Vrlo je konfigurabilan.

- Njegova izvedba je visoka u usporedbi s ARM-om.

- Podržava ga ugrađeni razvojni komplet.

- To je mekan mikroprocesor jezgra.

- Kako bi vam pomogao da brzo uredite svoju aplikaciju, ovaj procesor uključuje tri fiksne konfiguracije koje se odnose na dobro poznate klase procesora mikrokontroler, real-time i aplikacijski procesor.

Microblaze aplikacije

The primjene MicroBlaze-a uključuju sljedeće.

- Ovaj procesor ispunjava mnoge različite zahtjeve aplikacija kao što su industrijske, automobilske, medicinske i potrošačke, itd.

- Primjene MicroBlazea kreću se od jednostavnih automata stanja temeljenih na softveru do složenih kontrolera koji se koriste u ugrađenim aplikacijama ili uređajima koji se temelje na Internetu.

- Optimiziran je za ugrađene aplikacije poput industrijske kontrole, uredske automatizacije i automobila.

- MicroBlaze može komunicirati s velikim skupom perifernih uređaja kako bi se uklopio u aplikacije srednje veličine.

- Meka priroda ovog procesora čini ga prilagodljivim za različite primjene gdje dizajneri mogu zamijeniti značajke za veličinu kako bi ispunili ciljeve cijene i performansi za medicinske, automobilske, industrijske i sigurnosne aplikacije.

Dakle, ovo je sve o tome pregled Microblazea procesor. Ovo je potpuno opremljena, 32-bitna programabilna RISC meka procesorska jezgra. Ovaj procesor ispunjava različite zahtjeve unutar različitih područja kao što su potrošačka, medicinska, industrijska, automobilska i tržišta komunikacijske infrastrukture. Iznimno je konfigurabilan, pa se koristi kao ugrađeni procesor ili mikrokontroler unutar FPGA-a inače kao koprocesor za ARM. Ovdje je pitanje za vas, što je FPGA?