Dvije glavne vrste FET-ova koje trenutno postoje su: JFET-ovi i MOSFET-ovi.

MOSFET-ovi se mogu dalje klasificirati u vrstu iscrpljenosti i vrsta poboljšanja. Obje ove vrste definiraju osnovni način rada MOSFET-ova, dok je sam pojam MOSFET kratica od tranzistora s poljskim efektom metal-oksid-poluvodič.

S obzirom na činjenicu da dvije vrste imaju različite radne karakteristike, svaku ćemo od njih posebno procijeniti u različitim člancima.

Razlika između MOSFET-a za poboljšanje i iscrpljivanje

U osnovi, za razliku od MOSFET-ova za poboljšanje, MOSFET-ovi s istrošenim napajanjem su u stanju pripravnosti čak i uz prisutnost 0 V preko terminala od ulaza do izvora (VGS).

Za poboljšanje MOSFET-a, napon od vrata do izvora (VGS) mora biti iznad praga napona od vrata do izvora (VGS (th)) kako bi se ono provodilo .

Međutim, za MOSFET iscrpljenja N-kanala njegova VGS (th) vrijednost je iznad 0 V. To znači da čak i ako je VGS = 0 V, MOSFET iscrpljenosti može provoditi struju. Da biste ga isključili, VGS istrošenog MOSFET-a mora se smanjiti ispod VGS (th) (negativan).

U ovom ćemo sadašnjem članku razmotriti tip iscrpljivanja MOSFET, za koji se kaže da ima karakteristike koje se podudaraju s JFET-om. Sličnost je između granične vrijednosti i zasićenja u blizini IDSS.

Osnovna konstrukcija

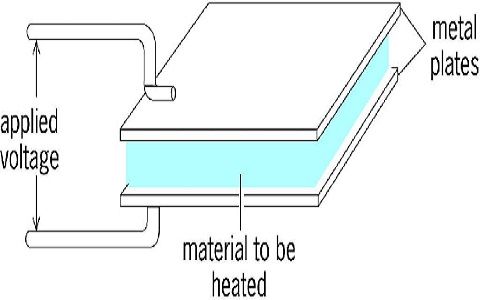

Slika 5.23 prikazuje osnovnu unutarnju strukturu MOSFET-a s osiromašenim kanalom.

Možemo pronaći blok p-tipa materijala stvoren pomoću silicijske baze. Taj se blok naziva supstrat.

Podloga je osnova ili temelj preko kojeg se gradi MOSFET. Za neke MOSFET-ove on je interno povezan s terminalom 'izvor'. Također, mnogi uređaji nude dodatni izlaz u obliku SS-a, koji sadrži 4-terminalni MOSFET, kao što je prikazano na slici 5.23.

Odvodni i izvorni priključci povezani su vodljivim kontaktima na n-dopirana mjesta i pričvršćeni kroz n-kanal, kao što je naznačeno na istoj slici.

Vrata su također povezana s metalnim slojem, iako su izolirana od n-kanala kroz fini sloj silicijevog dioksida (SiOdva).

SiOdvaposjeduje jedinstveni oblik izolacijskog svojstva nazvan dielektrik koji stvara suprotno električno polje u sebi kao odgovor na vanjsko primijenjeno električno polje.

Budući da je izolacijski sloj, materijal SiOdvanudi nam sljedeće važne informacije:

Kompletna izolacija je razvijena između terminala vrata i MOSFET kanala s ovim materijalom.

Štoviše, to je zbog SiOdva, kapija mosfet-a može imati izuzetno visok stupanj ulazne impedancije.

Zbog ovog vitalnog svojstva visoke ulazne impedancije, struja vrata IGje gotovo nula pojačala za bilo koju konfiguraciju MOSFET-a s prednamjenom DC.

Osnovni rad i karakteristike

KAO što se može vidjeti na slici 5.24, ulazni napon napona konfiguriran je na nula volti spajanjem dva terminala, dok napon VDSprimjenjuje se preko odvodne i izvorne stezaljke.

Uz gornju postavku, odvodna strana uspostavlja pozitivan potencijal slobodnih elektrona n-kanala, zajedno s ekvivalentnom strujom kroz JFET-kanal. Također, rezultirajuća struja VGS= 0V i dalje se identificira kao IDSS, kako je dato na slici 5.25

Vidimo da je na slici 5.26 napon izvora vrata VGSdaje negativni potencijal u obliku -1V.

Ovaj negativni potencijal pokušava prisiliti elektrone prema podlozi p-kanala (budući da se naboji odbijaju) i izvući rupe iz podloge p-kanala (budući da se privlače suprotni naboji).

Ovisno o veličini ove negativne pristranosti VGSse odvija rekombinacija rupa i elektrona što rezultira smanjenjem slobodnih elektrona u n-kanalu dostupnom za provođenje. Veće razine negativne pristranosti rezultiraju većom stopom rekombinacije.

Odvodna struja posljedično se smanjuje kako je gore navedeno negativno stanje pristranosti povećano, što je dokazano na slici 5.25 za VGSrazine VGS= -1, -2 i tako dalje, sve dok oznaka pinch-off ne bude -6V.

Odvodna struja kao rezultat zajedno s grafikonom krivulje prijenosa nastavlja se baš kao i kod a JFET.

Sada, za pozitivno VGSvrijednosti, pozitivna vrata privući će višak elektrona (slobodnih nosača) iz supstrata p-tipa, zbog reverzne struje curenja. To će uspostaviti svježe nosače putem rezultatskih sudara preko ubrzavajućih čestica.

Kako napon od vrata do izvora ima tendenciju porasta pozitivnom brzinom, odvodna struja pokazuje brzi porast, što je dokazano na slici 5.25 iz istih razloga kao što je gore spomenuto.

Razmak se razvio između krivulja VGS= 0V i VGS= +1 izrazito pokazuje iznos za koji se struja povećala zbog 1 - V varijacije VGS

Zbog brzog porasta odvodne struje moramo biti oprezni oko maksimalne struje, jer bi u protivnom mogla prijeći pozitivnu granicu napona na vratima.

Na primjer, za tip uređaja prikazan na slici 5.25, primjenom VGS= + 4V uzrokovalo bi porast odvodne struje na 22,2 mA, što možda prelazi maksimalnu granicu proboja (struje) uređaja.

Gornji uvjet pokazuje da upotreba pozitivnog napona od izvora do izvora generira pojačani učinak na količinu slobodnih nosača u kanalu, za razliku od VGS= 0V.

Zbog toga je područje pozitivnog napona na odvodu ili prijenosnim karakteristikama općenito poznato kao regija poboljšanja . Ovo područje leži između granične vrijednosti i razine zasićenja IDSSili regija iscrpljenosti.

Rješavanje primjera problema

Prednosti i primjena

Za razliku od MOSFET-ova u režimu poboljšanja, gdje nalazimo da odvodna struja pada na nulu kao odgovor na nulti napon od izvora do izvora, moderni FET u načinu iscrpljivanja ima primjetnu struju s nultim naponom na vratima. Da budemo precizni, otpor odvoda prema izvoru obično iznosi 100 Ohma u nultom naponu.

Kao što je naznačeno na gornjem grafikonu, RDS otpora ON(na)u odnosu na opseg analognog signala izgleda kao praktički ravni odgovor. Ova karakteristika, zajedno s razinama niske kapacitivnosti ovih naprednih uređaja s osiromašenjem, omogućuju im da budu posebno idealni kao analogni prekidači za audio i video prebacivanje.

MOSFET-ov način rada 'normalno uključeno' u načinu iscrpljivanja omogućava uređaju da bude savršeno pogodan za pojedinačne FET regulatore struje.

Jedan takav primjer sklopa može se vidjeti na sljedećoj slici.

Vrijednost Rs mogla bi se odrediti pomoću formule:

Rs= VGSisključiti[1 - (ID/ IDSS)1/2] / ID

gdje JaD je količina regulirane struje potrebna na izlazu.

Glavna prednost MOSFET-ova u načinu iscrpljivanja u aplikaciji s trenutnim izvorom je njihov minimalni odvodni kapacitet, što ih čini prikladnima za pristranske aplikacije u krugovima s malim ulaznim propuštanjem, srednjim brzinama (> 50 V / us).

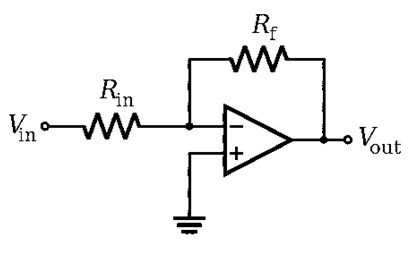

Donja slika prikazuje prednji kraj diferencijalne struje niskog ulaza propuštanja pomoću dvostruke funkcije FET niskog propuštanja.

Općenito govoreći, bilo koja strana JFET-a bit će pristrana na ID = 500 uA. Stoga je struja koja se može dobiti za kompenzaciju punjenja i zalutale kapacitete ograničena na 2ID ili, u ovakvim slučajevima, 1,0 mA. Odgovarajuće značajke JFET-a dokazane su proizvodnjom i osigurane su u tehničkom listu.

Cs simbolizira izlazni kapacitet izvor struje ulaznog stupnja 'rep'. Ovaj je kapacitet presudan za neinvertirajuća pojačala, s obzirom na činjenicu da ulazni stupanj doživljava značajnu razmjenu signala u cijeloj mreži, a struje punjenja u Cs mogu biti velike. U slučaju da se koriste normalni izvori struje, ovaj repni kapacitet mogao bi biti odgovoran za primjetno pogoršanje brzine porasta u neinvertirajućim krugovima (u usporedbi s invertirajućim aplikacijama, gdje su struje punjenja u Cs minimalne).

Pad stope porasta mogao bi se izraziti kao:

1/1+ (Cs / Sc)

Sve dok je Cs niži od Cc (kompenzacijski kondenzator), možda neće biti bilo kakvih varijacija u brzini porasta. U radu s DMOS FET-om C mogu biti oko 2 pF. Ova strategija donosi veliko poboljšanje stope porasta. Tamo gdje su potrebni trenutni deficiti veći od 1 do 5 mA, uređaj bi mogao biti pristran u načinu poboljšanja kako bi generirao čak 20 mA za maksimalni VGS od +2,5 V, s minimalnim izlaznim kapacitetom koji je i dalje ključni aspekt.

Sljedeća aplikacija u nastavku prikazuje odgovarajući strujni krug u načinu poboljšanja.

Analogni prekidač 'normalno-na' mogao bi se izraditi za zahtjeve u kojima standardni uvjeti postanu nužni tijekom nestanka napona napajanja, na primjer u automatskom rangiranju ispitnih alata ili za osiguravanje točnog pokretanja logičkih krugova pri prekidaču ON.

Smanjeni negativni napon praga uređaja nudi osnovne preduvjete za pogon i omogućuje rad s minimalnim naponom.

Donji krug pokazuje uobičajene čimbenike pristranosti za bilo koji analogni prekidač DMOS u načinu iscrpljivanja.

Da bi se uređaj isključio, na ulazu postaju nužni negativni naponi. Kad se to već kaže, otpor pri uključivanju mogao bi se svesti na najmanju mjeru kada se FET dodatno pojača pozitivnim naponom na vratima, što ga omogućuje posebno u području načina poboljšanja zajedno s područjem načina iscrpljivanja.

Ovaj odgovor može se vidjeti na sljedećem grafikonu.

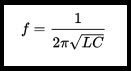

Visokofrekventno pojačanje jedinice, zajedno s njenim malim vrijednostima kapacitivnosti, donosi povećanu 'vrijednost zasluga'. To je zaista presudan element u VHF i UHF pojačavanju, koji određuje proizvod pojasa pojasa (GBW) FET-a, koji bi se mogao prikazati kao:

GBW = gfs / 2 Pi (Cu+ Cvan)

MOSFET tipa iscrpljivanja kanala

Konstrukcija MOSFET-a s osiromašenim kanalom savršena je naličje verzije s n-kanalima prikazana na sl. 5.23. Znači, supstrat sada ima oblik n-tipa, a kanal postaje p-tipa, kao što se može vidjeti na slici 5.28a dolje.

Identifikacija terminala ostaje nepromijenjena, ali napon i trenutni polariteti su obrnuti, kao što je naznačeno na istoj slici. Karakteristike odvoda bile bi točno onakve kakve su prikazane na sl. 5.25, osim VDSznak koji će u ovom slučaju dobiti negativnu vrijednost.

Odvodna struja IDpokazuje pozitivan polaritet i u ovom slučaju, to je zato što smo već preokrenuli njegov smjer. VGSpokazuje suprotni polaritet, što je i razumljivo, kao što je naznačeno na slici 5.28c.

Jer VGSje obrnuto stvara zrcalnu sliku za karakteristike prijenosa kao što je prikazano na slici 5.28b.

Znači, struja odvoda raste u pozitivnom VGSpodručje od granične točke na VGS= Vp dok jaDSS, onda nastavlja rasti kao negativna vrijednost VGSdiže se.

Simboli

Grafički znakovi za MOSFET tipa iscrpljenosti n- i p-kanala mogu se vidjeti na gornjoj slici 5.29.

Promatrajte način na koji odabrani simboli žele prikazati pravu strukturu uređaja.

Odsutnost izravne međusobne povezanosti (zbog izolacije vrata) između vrata i kanala simbolizira jaz između vrata i različitih terminala simbola.

Okomita crta koja predstavlja kanal pričvršćena je između odvoda i izvora, a podloga je 'drži'.

Dvije su skupine simbola na gornjoj slici za svaku vrstu kanala kako bi se naglasila činjenica da je na nekim uređajima podloga možda dostupna izvana, dok se na drugima to ne može vidjeti.

MOSFET (tip poboljšanja)

Iako MOSFET-ovi tipa osiromašenja i poboljšanja izgledaju slično sa svojim unutarnjim strukturama i funkcionalnim načinom rada, njihove se karakteristike mogu prilično razlikovati.

Glavna razlika je odvodna struja koja ovisi o određenoj razini napona od vrata do izvora za djelovanje prekida.

Točno, MOSFET tipa poboljšanja n-kanala može raditi s pozitivnim naponom vrata / izvora, umjesto s nizom negativnih potencijala koji obično mogu utjecati na MOSFET tipa osiromašenja.

Osnovna konstrukcija

MOSFET tipa poboljšanja n-kanala možete vizualizirati u sljedećem

Slika 5.31.

Odjeljak materijala tipa p izrađuje se kroz silicijsku bazu i, kako je prije naučeno, naziva se podlogom.

Ovaj je supstrat u nekim prilikama interno pričvršćen na izvornu iglu u MOSFET-u iscrpljujućeg tipa, dok je u nekim slučajevima završen kao četvrti vod zbog omogućavanja vanjske kontrole svoje potencijalne razine.

Izvodni i odvodni priključci spojeni su, kao i obično, pomoću metalnih kontakata na n-dopirana područja.

Međutim, možda će biti važno predočiti da na slici 5.31 nedostaje kanal između dva n-dopirana područja.

To se može smatrati osnovnom različitošću između unutarnjeg rasporeda MOSFET-a tipa osiromašenja i poboljšanja, odnosno odsutnosti inherentnog kanala koji bi trebao biti dio uređaja.

I dalje je uočljiv sloj SiO2, koji osigurava izolaciju između metalne baze terminala vrata i područja između odvoda i izvora. Međutim, ovdje se može svjedočiti kako stoji odvojen od odjeljka za materijal tipa p.

Iz gornje rasprave možemo zaključiti da unutarnji raspored MOSFET-a za trošenje i poboljšanje može imati neke sličnosti, osim nedostajućeg kanala između odvoda / izvora za vrstu poboljšanja MOSFET-a.

Osnovni rad i karakteristike

Za tip poboljšanja MOSFET kada se u njegov VGS uvede 0 V, zbog nedostajućeg n-kanala (za koji se zna da nosi puno slobodnih nosača), trenutni izlaz je nula, što je sasvim za razliku od tipa osiromašenja MOSFET-a, koji ima ID = IDSS.

U takvoj situaciji zbog nedostajuće putanje preko terminala odvod / izvor, velike količine nosača u obliku elektrona ne mogu se akumulirati u odvodu / izvoru (zbog n-dopiranih područja).

Primjenjujući pozitivan potencijal na VDS, s VGS postavljenim na nul volti i SS priključkom spojenim s izvornim priključkom, zapravo pronalazimo nekoliko obrnuto pristranih pn spojeva između n-dopiranih područja i p-podloge kako bismo omogućili bilo kakvo značajno provođenje preko odvod do izvora.

Na slici 5.32 prikazano je stanje u kojem se VDS i VGS primjenjuju s nekim pozitivnim naponom većim od 0 V, omogućujući odvodu i otvoru da imaju pozitivan potencijal u odnosu na izvor.

Pozitivni potencijal na vratima gura rupe u p-podlozi uz rub sloja SiO2 koji odlaze s mjesta i ulaze dublje u područja p-podloge, kao što je prikazano na gornjoj slici. To se događa zbog sličnih optužbi koje se međusobno odbijaju.

To rezultira stvaranjem područja iscrpljenja u blizini izolacijskog sloja SiO2 bez rupa.

Unatoč tome, elektroni p-supstrata koji su manjinski nosači materijala povlače se prema pozitivnom prolazu i počinju se skupljati u području blizu površine sloja SiO2.

Zbog svojstava izolacije sloja SiO2 negativni nosači omogućuju apsorpciju negativnih nosača na priključku vrata.

Kako povećavamo razinu VGS-a, tako se i elektronska gustoća blizu površine SiO2 povećava, sve dok konačno inducirano područje n-tipa nije u mogućnosti omogućiti kvantificirano provođenje kroz odvod / izvor.

Veličina VGS koja uzrokuje optimalno povećanje odvodne struje naziva se pragom napona, označeno simbolom VT . U tablicama ćete to moći vidjeti kao VGS (Th).

Kao što smo gore naučili, zbog odsutnosti kanala na VGS = 0 i 'poboljšane' pozitivnom primjenom napona od ulaza do izvora, ovaj tip MOSFET-a poznati su kao MOSFET-ovi poboljšanja.

Otkrit ćete da i MOSFET-ovi tipa iscrpljenja i poboljšanja pokazuju regije tipa poboljšanja, ali izraz poboljšanje koristi se za potonje jer posebno radi koristeći način rada za poboljšanje.

Sada, kada se VGS potisne preko praga, koncentracija slobodnih nosača će porasti u kanalu u kojem je inducirana. To dovodi do povećanja odvodne struje.

S druge strane, ako VGS održavamo konstantnim i povećavamo razinu VDS (napon odvoda do izvora), to će u konačnici dovesti do toga da MOSFET dosegne svoju točku zasićenja, kao što bi se to uobičajeno dogodilo s bilo kojim JFET-om ili MOSFET-om za trošenje.

Kao što je prikazano na slici 5.33, ID odvodne struje izravnava se uz pomoć postupka priklještenja, naznačenog užim kanalom prema odvodnom kraju induciranog kanala.

Primjenom primjene Kirchhoffova zakona napona na napone stezaljki MOSFET-a na slici 5.33, dobivamo:

Ako se VGS održava konstantnim na određenu vrijednost, na primjer 8 V, a VDS podigne s 2 na 5 V, napon VDG za jednadžbu 5.11 može se vidjeti kako pada sa -6 na -3 V, a potencijal vrata postaje sve manje pozitivan s obzirom na odvodni napon.

Ovaj odgovor zabranjuje povlačenje slobodnih nosača ili elektrona prema ovom području induciranog kanala, što zauzvrat rezultira padom efektivne širine kanala.

U konačnici, širina kanala smanjuje se do točke priklještenja, dostižući stanje zasićenja slično onome što smo već naučili u našem ranijem MOSFET članku o iscrpljivanju.

Znači, daljnje povećanje VDS-a s fiksnim VGS-om ne utječe na razinu zasićenja ID-a, sve dok se ne dosegne situacija kvara.

Gledajući sliku 5.34 možemo identificirati da se za MOSFET kao na slici 5.33 koji ima VGS = 8 V, zasićenje odvija na VDS razini od 6 V. Da bismo bili precizni, razina zasićenja VDS povezana je s primijenjenom razinom VGS pomoću:

Bez sumnje, to implicira da će, kada je vrijednost VT fiksna, povećanje razine VGS proporcionalno uzrokovati više razine zasićenja VDS-a kroz lokus razine zasićenja.

Pozivajući se na karakteristike prikazane na gornjoj slici, razina VT je 2 V, što je vidljivo činjenicom da je odvodna struja pala na 0 mA.

Stoga obično možemo reći:

Kad su VGS vrijednosti manje od granične razine za MOSFET tipa poboljšanja, njegova odvodna struja je 0 mA.

Također možemo jasno vidjeti na gornjoj slici da, sve dok je VGS povišen s VT na 8 V, odgovarajuća razina zasićenja za ID također se povećava s 0 na 10 mA.

Štoviše, možemo nadalje primijetiti da se razmak između razina VGS povećava s povećanjem vrijednosti VGS, što uzrokuje beskonačno rastuće prirastke odvodne struje.

Otkrivamo da je vrijednost odvodne struje povezana sa naponom od ulaza do izvora za VGS razine koje su veće od VT, kroz sljedeći nelinearni odnos:

Izraz koji je prikazan u zagradama u kvadratu izraz je koji je odgovoran za nelinearnu povezanost između ID-a i VGS-a.

Izraz k je konstanta i funkcija je rasporeda MOSFET-a.

Vrijednost ove konstante k možemo saznati putem sljedeće jednadžbe:

pri čemu su ID (uključeno) i VGD (uključeno) vrijednosti posebno ovisno o karakteristikama uređaja.

Na slijedećoj slici 5.35 dolje nalazimo da su karakteristike odvoda i prijenosa poredane jedna pored druge kako bi se razjasnio postupak prijenosa.

U osnovi je sličan postupku koji je prethodno objašnjen za JFET i MOSFET-ove tipa osiromašenja.

Međutim, u ovom slučaju moramo imati na umu da je odvodna struja 0 mA za VGS VT.

Ovdje ID može vidjeti primjetnu količinu struje, koja će se povećati kako je određeno jednadžbom. 5.13.

Napomena, dok definiramo točke preko karakteristika prijenosa iz karakteristika odvoda, uzimamo u obzir samo razine zasićenja. Ovo ograničava područje rada na VDS vrijednosti veće od razine zasićenja utvrđene jednadžbom. (5,12).

MOSFET-ovi tipa p-kanala za poboljšanje

Struktura MOSFET-a tipa poboljšanja p-kanala, kako je prikazano na slici 5.37a, upravo je suprotna onoj prikazanoj na slici 5.31.

Znači, sada ste otkrili da je supstrat n-tipa i p-dopirana područja ispod odvodnih i izvornih spojeva.

Stezaljke su i dalje onako kako su uspostavljene, ali su svi trenutni smjerovi i polariteti napona obrnuti.

Karakteristike odvoda mogu izgledati kao dane na slici 5.37c, s povećanim količinama struje uzrokovanim kontinuirano negativnijim veličinama VGS-a.

Karakteristike prijenosa bile bi zrcalni otisak (oko osi ID) krivulje prijenosa sa slike 5.35, s povećanjem ID-a sa sve više i više negativnih vrijednosti VGS-a iznad VT-a, kao što je prikazano na slici 5.37b. Jednadžbe (5.11) do (5.14) slično su primjerene p-kanalnim uređajima.

Reference:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Prethodno: Krug anti-špijunskog RF detektora - bežični detektor grešaka Dalje: Karakteristike prijenosa