Proces dizajniranja digitalnog hardvera intenzivno se transformirao tijekom posljednjih nekoliko godina. Dakle, mali digitalni sklopovi mogu se implementirati pomoću PAL-a i PLA-a. Koristi se svaki uređaj za provedbu raznih sklopova kojima ne treba više od broja i / ps, o / ps i uvjeta proizvoda koji se nude u određenom čipu. Ovi čipovi nisu prikladni za prilično skromne veličine, obično podržavaju uzajamni broj ulaza i izlaza ne veći od 32. Za projektiranje ovih krugova kojima je potrebno više ulaza i izlaza, mogu se upotrijebiti brojni PLA / PAL-ovi ili pak otmjeniji tip čipa može se koristiti pod nazivom CPLD (složeni programibilni logički uređaj). CPLD čip uključuje nekoliko blokova sklopova na jednom čipu s unutarnjim resursima ožičenja za pričvršćivanje blokova krugova. Svaki blok sklopa usporediv je s PLA ili PAL.

Što je složeni programirljivi logički uređaj?

Skraćenica CPLD je 'Složeni programibilni logički uređaji', to je jedan vrsta integriranog kruga koje dizajneri aplikacija dizajniraju za primjenu digitalnog hardvera poput mobilnih telefona. Oni se mogu nositi sa svjetski višim dizajnom od SPLD-a (jednostavnih programabilnih logičkih uređaja), ali nude manje logike od FPGA-a ( poljski programibilni nizovi vrata ) .CPLD-ovi uključuju brojne logičke blokove, a svaki od njih sadrži 8-16 makroćelija. Budući da svaki logički blok izvršava određenu funkciju, sve su makroćelije u logičkom bloku u potpunosti povezane. Ovisno o uporabi, ovi blokovi mogu biti povezani, a možda i ne.

Složeni programirljivi logički uređaj

Većina CPLD-ova (složeni programibilni logički uređaji) imaju makroćelije sa zbrojem logičke funkcije i izbornog predmeta FF (japanke) . Ovisno o čipu, kombinatorna logička funkcija podržava od 4 do 16 izraza proizvoda s uključivanjem ventilatora. CPLD se također razlikuju u pogledu registara smjene i logičkih vrata. Iz tog razloga, CPLD-ovi s ogromnim brojem logičkih ulaza mogu se koristiti umjesto FPGA-a. Druga CPLD specifikacija označava broj izraza proizvoda koje makroćelija može postići. Pojmovi proizvoda produkt su digitalnih signala koji izvršavaju određenu logičku funkciju.

CPLD su dostupni u nekoliko obrazaca IC paketa i logičkih porodica. CPLD se također razlikuju u pogledu napona napajanja, radne struje, struje u stanju pripravnosti i rasipanja snage. Osim toga, oni se mogu dobiti s raznim količinama memorije i raznim vrstama memorijske podrške. Obično se memorija izražava u bitovima / megabitima. Podrška za memoriju sastoji se od ROM-a, RAM-a i RAM-a s dva porta. Također se sastoji od CAM (memorija koja se može adresirati sadržajem), kao i FIFO (prvi ulaz, prvi izlaz) i LIFO (zadnji ulaz, zadnji izlaz) memorija.

Arhitektura složenog programabilnog logičkog uređaja

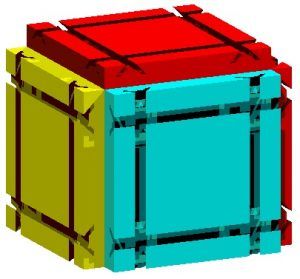

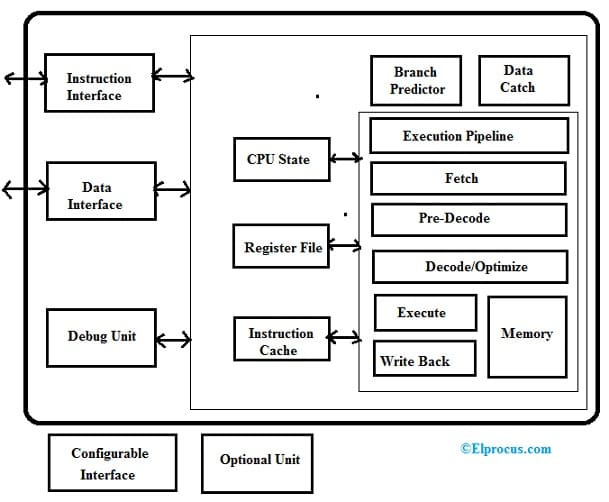

Složeni programibilni logički uređaj sastoji se od skupine programabilnih FB-a (funkcionalnih blokova). Ulazi i izlazi ovih funkcionalnih blokova povezani su zajedno GIM-om (globalna matrica međusobnog povezivanja). Ova matrica međusobnog povezivanja može se ponovno konfigurirati, tako da možemo mijenjati kontakte između funkcionalnih blokova. Bit će nekih ulaznih i izlaznih blokova koji će nam omogućiti da CPLD ujedinimo s vanjskim svijetom. Arhitektura CPLD prikazana je u nastavku.

Općenito, programabilni FB izgleda kao niz logičkih vrata , gdje se niz AND ulaza može programirati, a ILI vrata su stabilna. Ali, svaki proizvođač razmišlja kako dizajnirati funkcionalni blok. Navedeni o / p može se pronaći upravljanjem povratnim signalima postignutim na izlazima OR ulaza.

CPLD arhitektura

U programiranju CPLD, dizajn se prvo kodira u jeziku Verilog ili VHDL nakon što se kod (simulira i sintetizira. Tijekom sinteze odabere se model CPLD (ciljni uređaj) i stvori mrežni popis za mapiranje. Ovaj popis može biti blizak -prilagođavanje izvornoj CPLD arhitekturi korištenjem procesa mjesta i rute, obično postignutog softverom mjesta i rute vlasništva tvrtke CPLD. Tada će operater izvršiti neke postupke potvrde. Ako je sve u redu, on će koristiti CPLD, inače on će ga preurediti.

Arhitektonska pitanja CPLD-a

Pri razmatranju složenog programabilnog logičkog uređaja za upotrebu u dizajnu, mogu se uzeti u obzir sljedeći arhitektonski problemi

- Programska tehnologija

- Sposobnost funkcijskog bloka

- Sposobnost I / O

Uključuju neke od obitelji CPLD-a iz različitih trgovaca

- Altera MAX 7000 i MAX 9000 obitelji

- Atmel ATF i ATV obitelji

- Rešetka isp LSI obitelj

- Rešetka (Vantis) obitelj MACH

- Obitelj Xilinx XC9500

Obitelji CPLD-a

Primjene CPLD-a

Primjene CPLD-ova uključuju sljedeće

- Složeni programibilni logički uređaji idealni su za kritične upravljačke programe visokih performansi.

- CPLD se može koristiti u digitalnom dizajnu za obavljanje funkcija boot loader-a

- CPLD se koristi za učitavanje podataka o konfiguraciji poljskog programabilnog polja vrata iz trajne memorije.

- Općenito se koriste u malim dizajnerskim aplikacijama poput dekodiranja adresa

- CPLD-ovi se često koriste u mnogim aplikacijama, poput prijenosnih uređaja osjetljivih na cijenu i baterija, zbog male veličine i upotrebe male snage.

Dakle, ovdje se radi o složenoj programabilnoj arhitekturi logičkih uređaja i njezinim aplikacijama. Nadamo se da ste bolje razumjeli ovaj koncept. Nadalje, bilo kakva pitanja u vezi s ovim konceptom ili za provedbu bilo kakvih električnih i elektroničkih projekata , dajte svoje vrijedne prijedloge komentirajući u odjeljku za komentare u nastavku. Evo pitanja za vas, koja je razlika između CPLD i FPGA?

Foto bodovi:

- CPLD wikimedia

- Arhitektura CPLD-a slidesharecdn